Ph.D. Program in Smart Computing

Dipartimento di Ingegneria dell'Informazione (DINFO) Dipartimento di Ingegneria dell'informazione e Scienze Matematiche (DIISM)

# Reconfigurable Architectures for Accelerating Distributed Applications

A Graph Processing Application Case Study

Amin Sahebi

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Smart Computing

*Ph.D. Program in Smart Computing University of Florence, University of Pisa, University of Siena*

# Reconfigurable Architectures for Accelerating Distributed Applications

A Graph Processing Application Case Study

### Amin Sahebi

Advisor:

Prof. Roberto Giorgi

Head of the Ph.D. Program:

Prof. Stefano Berretti

**Evaluation Committee:**

Prof. Tullio Vardanega, *Università degli Studi di Padova, UNIPD* Prof. Alessandro Lonardo, *Instituto Nazionale di Fisica Nucleare (INFN)*

XXXIV ciclo — January 2022

Copyright © 2022 by Amin Sahebi.

### Acknowledgments

I want to first thank my supervisor Prof. Roberto Giorgi, and sincerely appreciate how he has been continuously encouraging and guiding me in these three years, and also how he has always been available, supportive of all of my efforts and struggles.

I want to thank my fiancé, Parisa, my life support and courage, this work could not be done without her all the motivation, support and love sent to me. I'm also grateful to my family, my parents, my lovely sister, and my brothers for their consistent support.

Then, I would like to thank my Supervisory Committee for their help, feedback, and suggestions within three phases of my annual evaluations. Prof. Antonio Prete from the University of Pisa and Prof. Sandro Bartolini from the University of Siena, plus the reviewers and evaluation committee members, Prof. Tullio Vardanega from Università degli Studi di Padova (UNIPD), and Prof. Allesandro Lonardo from Instituto Nazionale di Fisica Nucleare (INFN) for their insightful comments and suggestions to extremely strengthen the quality of this thesis.

In the last year of my Ph.D. I had this opportunity to spend 6 months as visiting researcher in a foreign institution. I took this opportunity and collaborated with the "Custom Computing Research Center" at Imperial College London, UK. Indeed, it was a great and fruitful collaboration. I want to thank Prof. Wayne Luk for his kind advise and admitted me to join his group and Prof. Georgi Gaidajiev for his suggestions and guidance throughout the collaboration. I am also thankful to Dear Marco Barbone for his kind suggestions, collaboration, and availability. As I have been admitted in as Smart Computing Program as a Ph.D. candidate with the "Regione Toscana scholarship", I also would like to thank "Regione Toscana" for the Pegaso grant. Moreover, this thesis is partly funded by the European Commission on AXIOM H2020 (id. 645496), TERAFLUX (id. 249013), and HiPEAC (id. 871174).

In addition, I would like also appreciate "Xilinx University Program" for their kind hardware donation to the University of Siena and giving me the access to the XACC Xilinx Adaptive Computing Cluster in the ETH Zürich center.

Siena, Italy January 2022 Amin

### Contents

| С  | onten | ts                                                                | v   |

|----|-------|-------------------------------------------------------------------|-----|

| Li | st of | Figures                                                           | vii |

| Li | st of | Tables                                                            | xi  |

| 1  | Intr  | oduction                                                          | 1   |

|    | 1.1   | Motivation and contribution                                       | 2   |

|    | 1.2   | Thesis Structure                                                  | 2   |

| 2  | Rela  | ated works                                                        | 5   |

|    | 2.1   | Dataflow architecture                                             | 6   |

|    | 2.2   | Taxonomy of dataflow execution models                             | 6   |

|    | 2.3   | Fine-grained Parallelism Approaches in Dataflow Architecture      | 11  |

|    | 2.4   | Dataflow Runtime Libraries                                        | 14  |

|    | 2.5   | Dataflow Execution Models using Hardware Accelerator              | 16  |

| 3  | Dat   | aflow Execution Model Baseline Study                              | 21  |

|    | 3.1   | Methodology                                                       | 22  |

|    | 3.2   | Reference code and Hardware                                       | 24  |

|    | 3.3   | Environment, Compilers, and Setups                                | 24  |

|    | 3.4   | Literature Study                                                  | 27  |

|    | 3.5   | Recursive Fibonacci                                               | 28  |

|    | 3.6   | Blocked Matrix Multiplication                                     | 38  |

|    | 3.7   | Blocked Cholesky Factorization                                    | 44  |

|    | 3.8   | Histogram                                                         | 48  |

|    | 3.9   | Conclusion                                                        | 52  |

| 4  | Dat   | aflow Runtime                                                     | 53  |

|    | 4.1   | DRT: A Lightweight Dataflow Runtime To Debug and Develop Dataflow |     |

|    |       | Programs                                                          | 53  |

|    |       | 4.1.1 Background                                                  | 53  |

|    |       | 4.1.2 Writing dataflow codes with the DF-Threads API              | 55  |

|    |       | 4.1.3 Introducing DRT                                             | 57  |

|    |       | 4.1.4 Evaluation                                                  | 59  |

.

| 5  | Prop  | posal for a Distributed Large Scale Graph Processing on multi-FPGA Plat- |     |

|----|-------|--------------------------------------------------------------------------|-----|

|    | forn  | n                                                                        | 63  |

|    | 5.1   | Introduction                                                             | 63  |

|    | 5.2   | Background and Motivation                                                | 66  |

|    | 5.3   | Related Work                                                             | 66  |

|    | 5.4   | Hardware Implementation                                                  | 71  |

|    |       | 5.4.1 Host Program                                                       | 71  |

|    |       | 5.4.2 FPGA Kernels                                                       | 72  |

|    | 5.5   | Evaluation and Performance Model                                         | 78  |

|    | 5.6   | Conclusion                                                               | 80  |

| 6  | Data  | aflow Case Studies                                                       | 83  |

|    | 6.1   | A Dataflow Methodology for Accelerating FFT                              | 83  |

|    |       | 6.1.1 Introduction and Theoretical background                            | 83  |

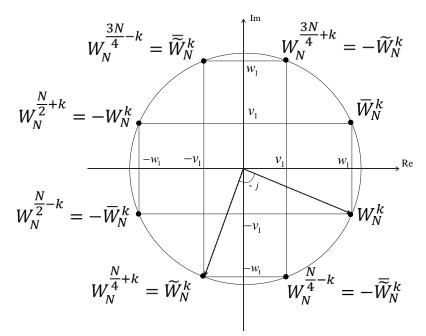

|    |       | 6.1.2 Reducing the needed twiddle factors                                | 85  |

|    |       | 6.1.3 The 8-point FFT Data-Flow Graph                                    | 86  |

|    |       | 6.1.4 Experimental validation                                            | 88  |

|    |       | 6.1.5 Related work                                                       | 89  |

|    |       | 6.1.6 Conclusion and future works                                        | 90  |

| 7  | A Cı  | ustom Board To Perform Distributed Computing                             | 91  |

|    | 7.1   | Gluon: The High-Speed Interconnect Solution                              | 91  |

|    | 7.2   | Conclusion                                                               | 93  |

| 8  | Con   | clusion and Future Studies                                               | 95  |

| Bi | bliog | raphy                                                                    | 97  |

| Α  | Арр   | endix A - Publications                                                   | 111 |

|    | A.1   | Peer-reviewed Conference Papers                                          | 111 |

|    | A.2   | Workshops and Posters                                                    | 111 |

| A  | Арр   | endix B - Parallel Programming Models Notes                              | 113 |

|    | A.1   | MPI profiling with mpiP                                                  | 113 |

|    | A.2   | Pure OpenMPI on Hyper threaded Hardware                                  | 117 |

|    | A.3   | Scripts                                                                  | 118 |

# List of Figures

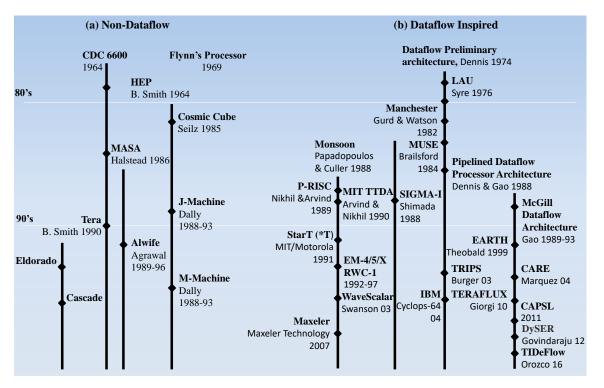

| 2.1 | The most influential dataflow inspired and non-dataflow architectures and their timeline.                                                                                                                                                | 7  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

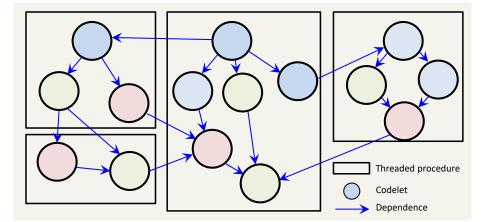

| 2.2 | A codelet Graph (CDG) shows the codelets and their dependencies connected                                                                                                                                                                | 10 |

| 2.3 | through a multiple threaded blocks linked together [141]                                                                                                                                                                                 | 13 |

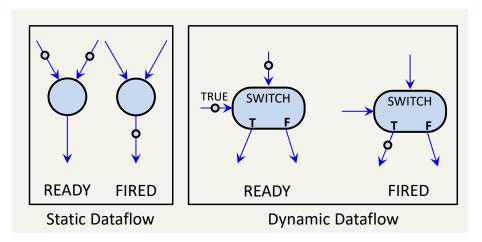

| 2.0 | dataflow.                                                                                                                                                                                                                                | 13 |

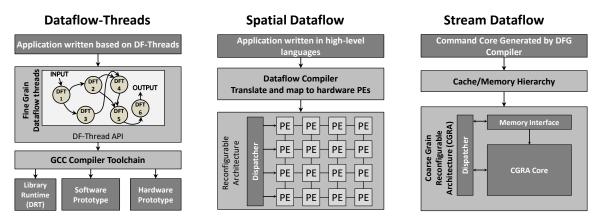

| 2.4 | The Dataflow Thread execution model high-level architecture versus well-<br>known modern dataflow approaches.                                                                                                                            | 17 |

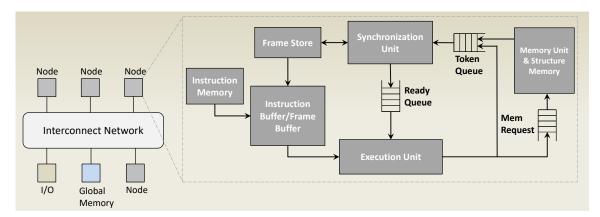

| 2.5 | The abstract model of the processing node using dynamic dataflow along with synchronization unit proposed in [130] and [129].                                                                                                            | 17 |

| 2.6 | The dataflow RISC multiprocessor organization proposed in [109]. In this work<br>the dataflow semantics and its instruction set based on I-structure method is<br>mapped to the RISC processor.                                          | 17 |

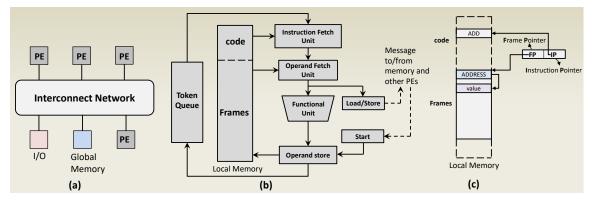

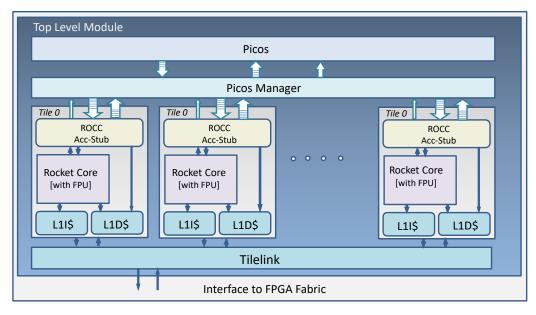

| 2.7 | RISC-V Dataflow Extension instruction illustration in (a) and (b) presented in [35]. (c) shows the dataflow token. Here the tag is used to match operands that are part of the same instruction; for example, if an instruction includes |    |

|     | two operands, both of them will have the same tag.                                                                                                                                                                                       | 19 |

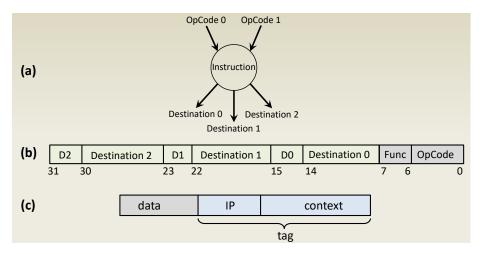

| 2.8 | An overview of the Picos and Rocket chip system architecture [108]                                                                                                                                                                       | 19 |

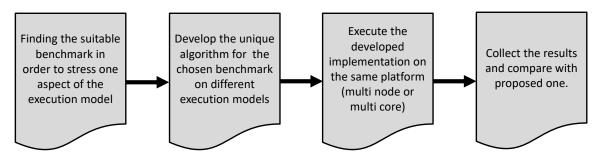

| 3.1 | The methodology to develop the desired baseline.                                                                                                                                                                                         | 23 |

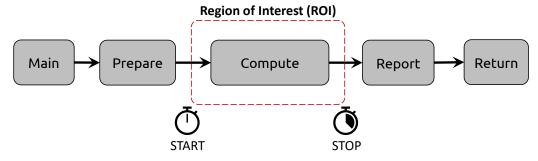

| 3.2 | The separated functions development in all algorithms and programming models to ensure Region of Interest measures the same part of the algorithm                                                                                        |    |

|     | in all benchmarks.                                                                                                                                                                                                                       | 23 |

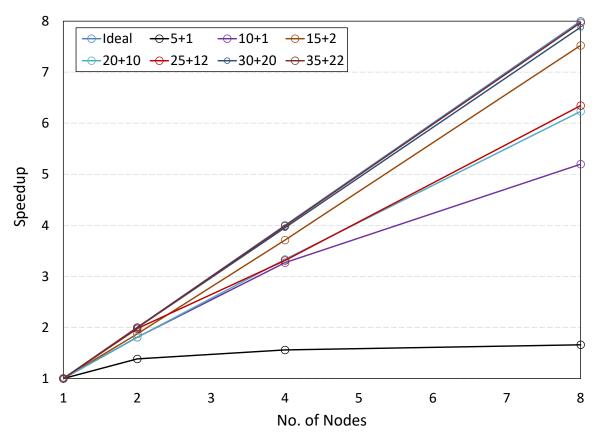

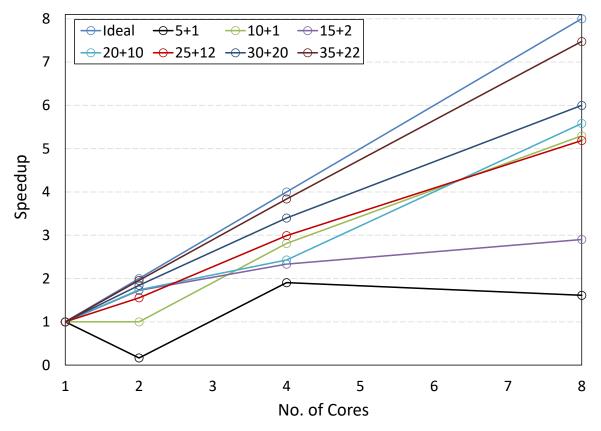

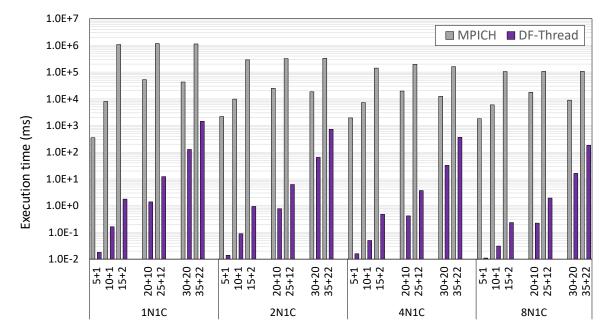

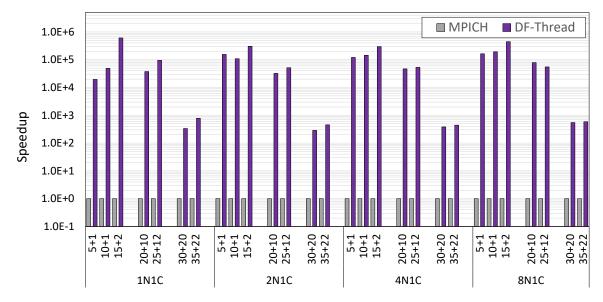

| 3.3 | The speedup of the DF-Thread in the multi-node experiment.                                                                                                                                                                               | 33 |

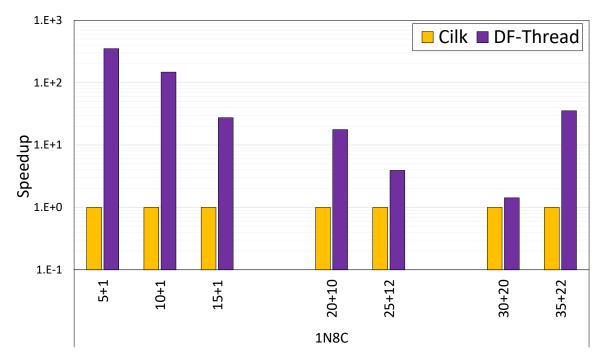

| 3.4 | The speedup of the DF-Thread in the multi-core experiment                                                                                                                                                                                | 34 |

| 3.5 | The RFIB multi-node experiment within DF-Thread and MPI. The baseline<br>is MPI and we show how DF-Thread is comparable within the well-known                                                                                            | •  |

| 2   | programming model for variety of RFIB indexes.                                                                                                                                                                                           | 36 |

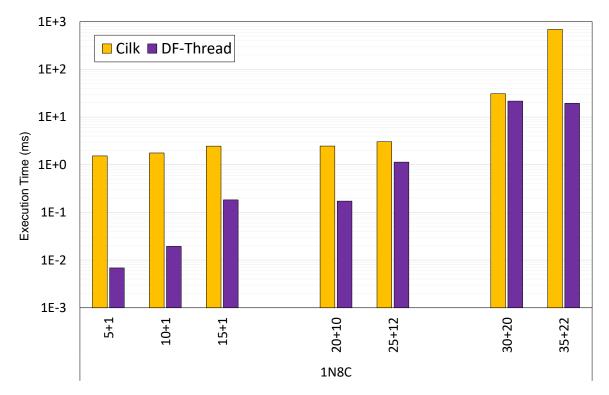

| 3.6 | The Execution time comparison of DF-Threads against Cilk with the RFIB experiment on 8 cores experiment.                                                                                                                                 | 37 |

| 3.7 | The scalability of DF-Threads against Cilk with the RFIB experiment on 8 cores experiment.                                                                                                                                               | 37 |

| 3.8 | The RFIB multi-node experiment within DF-Thread and MPICH. Here we show how much is the Speedup of DF-Thread compared to MPI execution model.                                                                                            |    |

|     |                                                                                                                                                                                                                                          |    |

.

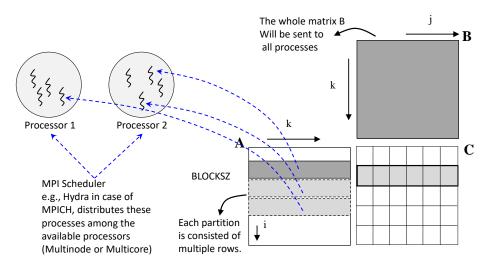

| 3.9  | The Blocked Matrix Multiplication algorithm sketch that is used in our bench-<br>mark and its execution model                                                                                                                                                                                                                                                                                                                                                                                         | 38       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

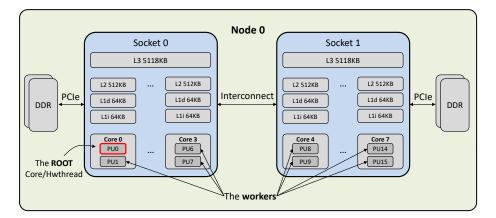

| 3.10 | A sample structure of the hardware and how MPI processes are distributed throughout the hardware resources.                                                                                                                                                                                                                                                                                                                                                                                           | 39       |

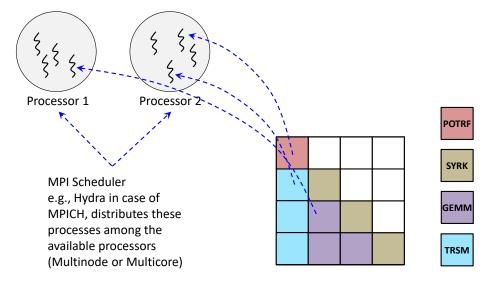

| 3.11 | Scheme of the Blocked Cholesky and how kernels are distributed throughout the hardware resources.                                                                                                                                                                                                                                                                                                                                                                                                     | 39<br>44 |

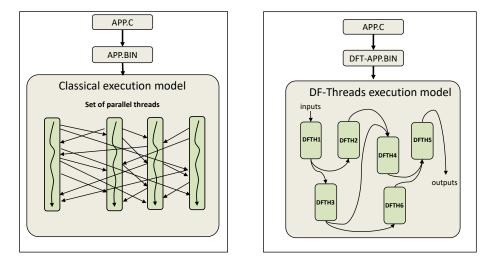

| 4.1  | Simplified representation of the DF-Threads execution model. On the left, we represent the irregular read and write of generic threads. On the right, the exchange of data among threads happens in a more regular fashion [88]                                                                                                                                                                                                                                                                       | 54       |

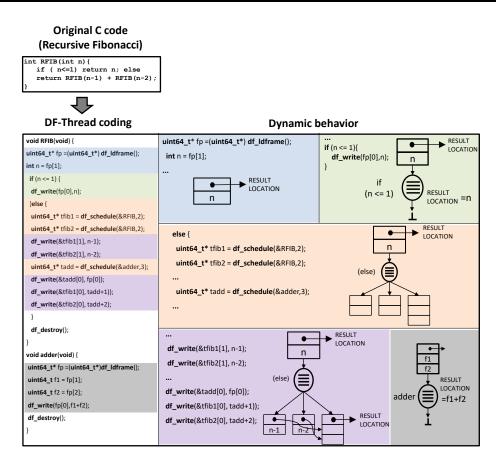

| 4.2  | Illustrating the operations of the basic DRT API functions with a simple Recursive Fibonacci (RFIB) example. On the left, there is the representation of the RFIB function and its coding in DF-Thread style. On the right, we detail the                                                                                                                                                                                                                                                             |          |

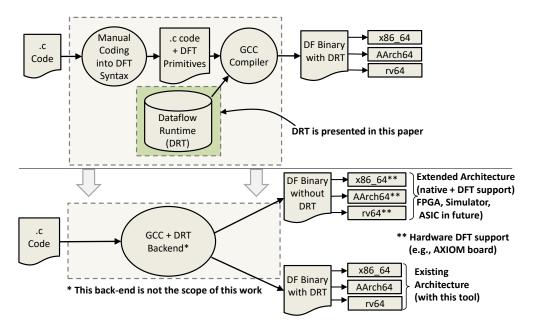

| 4.3  | specific dynamic behavior. Example rearranged from [104]                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56       |

| 4.4  | <ul> <li>idea is that DRT could help develop a future DRT backend of a standard compiler.</li> <li>DRT sample output. DRT_DEBUG is an environment variable for specifying the debug</li> <li>level. The DF-Threads functions are mapped to internal operations where TS stands for</li> <li>thread scheduling, TE stands for thread-end, TD stands for thread drop, TW stands</li> <li>for thread write, <i>ip</i> stands for instruction pointer, and <i>fp</i> stands for frame pointer.</li> </ul> | 56       |

| 4.5  | Other debugging information is <i>fi</i> for frame index, <i>sc</i> stands for synchronization count, <i>ipnew/fpnew</i> are the <i>ip/fp</i> just freed                                                                                                                                                                                                                                                                                                                                              | 58       |

| 4.6  | is in ready or waiting status                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58       |

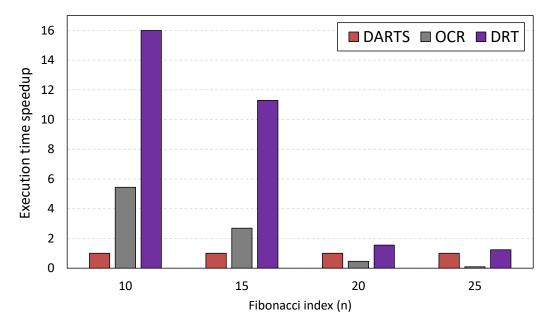

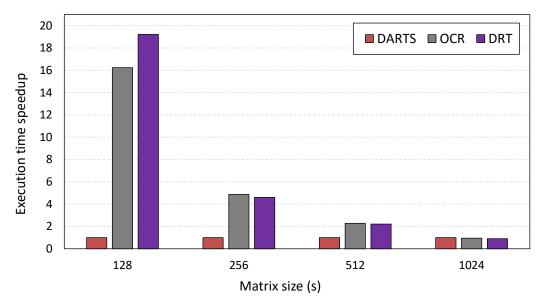

| 4.7  | <ul> <li>runtime. Here OCR is the baseline. DRT reaches better performance due to a simplified management of the dataflow execution.</li> <li>Blocked Matrix Multiplication execution time speedup comparison between DRT and DARTS and OCR, with the DARTS as baseline. While for larger Matrix</li> </ul>                                                                                                                                                                                           | 60       |

|      | sizes the execution time tends to be the same for three tools, it is important to<br>note that during the development-cycle, we typically use smaller inputs. So,<br>the shorter execution time of DRT during tests helps focus on the development.                                                                                                                                                                                                                                                   | 61       |

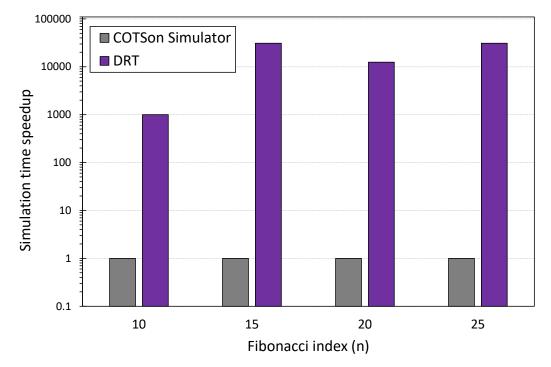

| 4.8  | Simulation time speedup comparison between DRT and the COTSon simulator<br>by using the RFIB example. DRT significantly decreases the development-cycle<br>time to develop a dataflow program.                                                                                                                                                                                                                                                                                                        | 62       |

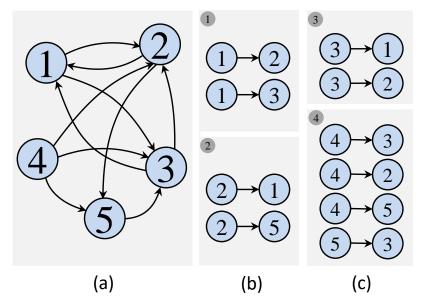

| 5.1  | Graph partitioning scheme used in our system preprocessing method. Figure (a) shows a sample graph, Figure (b) and Figure (c) show the partitioned edge into 2 chunks which inside each chunk there are 2 blocks therefore in total we                                                                                                                                                                                                                                                                |          |

|      | have 4 blocks of edge which is shown in each block.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69       |

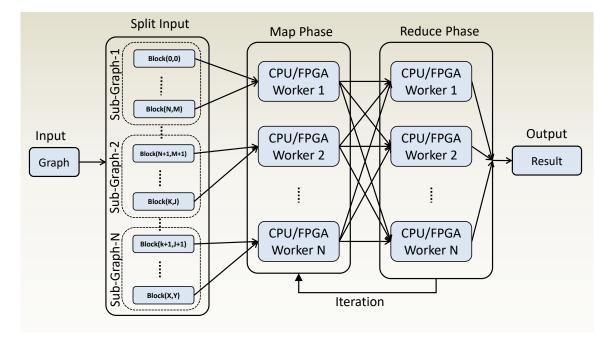

| 5.2  | The Hadoop framework for distributed graph processing high-level overview.                               | 71  |

|------|----------------------------------------------------------------------------------------------------------|-----|

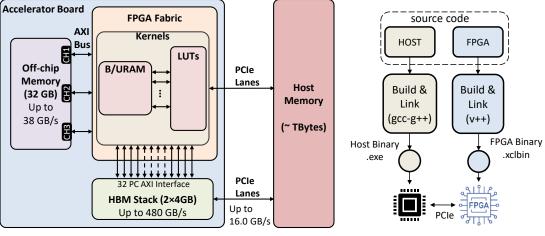

| 5.3  | The Alveo card harwdare accelerator hardware and its compilation framework.                              | 72  |

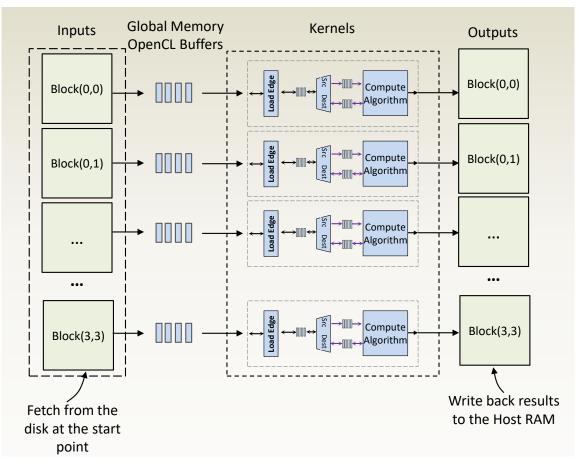

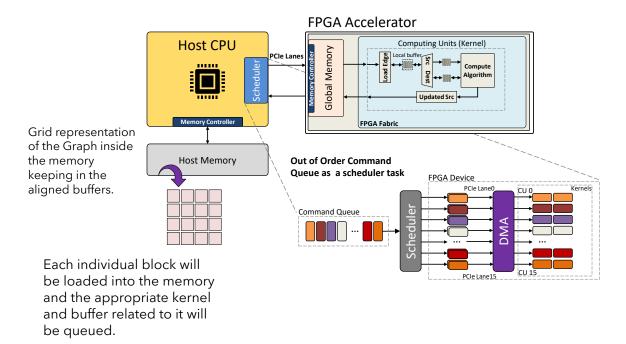

| 5.4  | The Host software is responsible to drive kernel and dispatch data between                               |     |

|      | CPU and Hardware accelerator                                                                             | 73  |

| 5.5  | The hardware implementation high-level overview.                                                         | 77  |

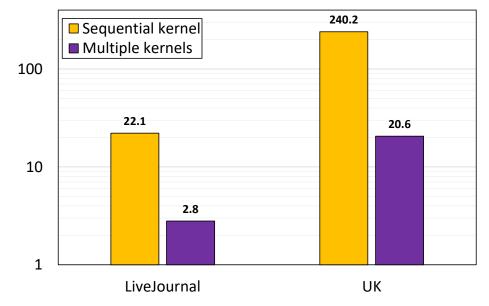

| 5.6  | The speedup gained while using multiple kernel instances against running the                             |     |

|      | application using sequential kernel                                                                      | 78  |

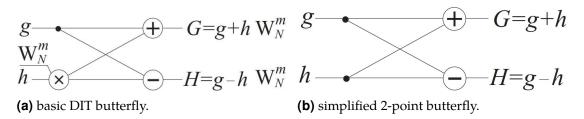

| 6.1  | Twiddle factor position for a length-2 DFT.                                                              | 84  |

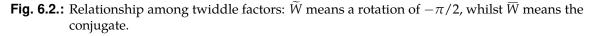

| 6.2  | Relationship among twiddle factors: $\widetilde{W}$ means a rotation of $-\pi/2$ , whilst $\overline{W}$ |     |

|      | means the conjugate.                                                                                     | 85  |

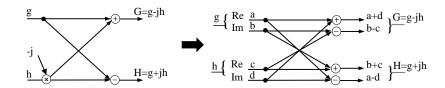

| 6.3  | Eliminating Complex Multiplication based on our proposed method.                                         | 86  |

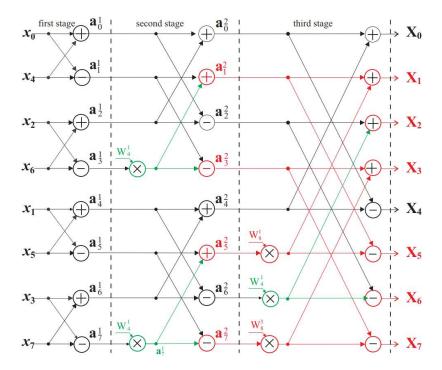

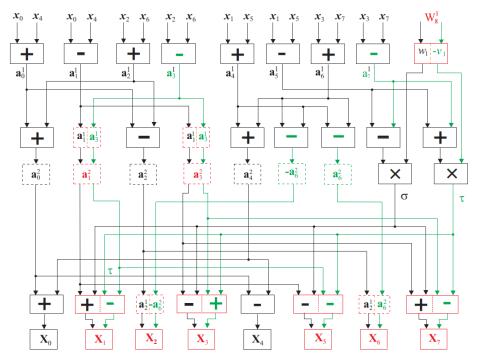

| 6.4  | 8-point butterfly FFT.                                                                                   | 87  |

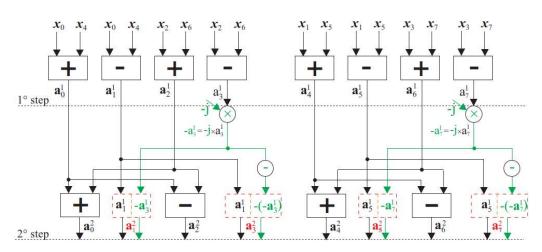

| 6.5  | Data-Flow Program Graph (DPG) for the first two steps                                                    | 87  |

| 6.6  | DPG after the third step                                                                                 | 89  |

| 7.1  | The cluster of FPGAs using Gluon boards. The network is capable of creating                              |     |

|      | different network topologies such as Mesh, Star, 2D-Torus etc.                                           | 92  |

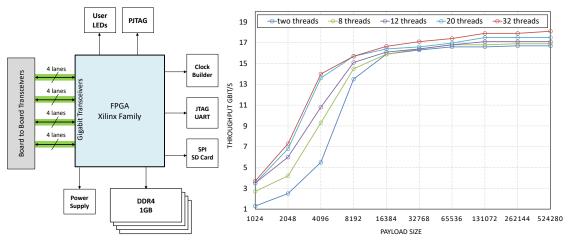

| 7.2  | Gluon board block diagram and throughput to test the functionality of the                                |     |

|      | board                                                                                                    | 92  |

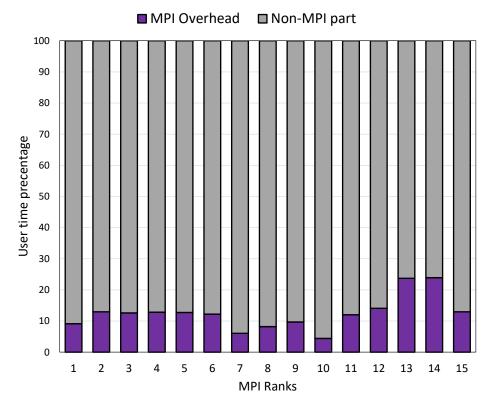

| A.1  | Results of profiling BMM with MPI shows an example of the MPI overhead                                   |     |

| 11.1 | over 15 cores, it can be seen from the results that most of the workers have                             |     |

|      | unbalanced MPI overhead across available resources, and in this case not                                 |     |

|      | having a ideal speedup. (Experiment has been done on TFX2)                                               | 116 |

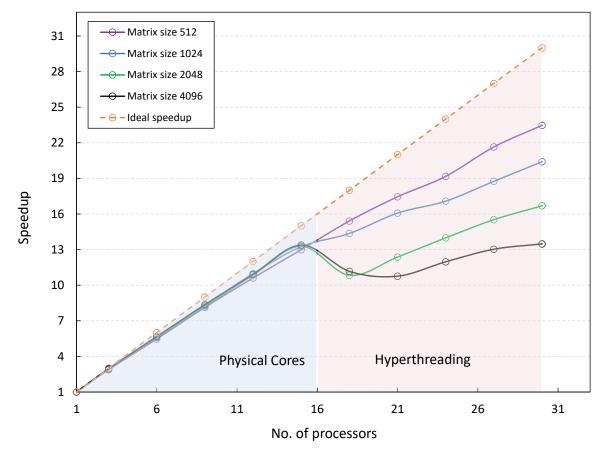

| A.2  | Results obtained from the BMM with OpenMPI with different Matrix sizes.                                  |     |

|      | It turns out while the second thread of the core is calling, the performance                             |     |

|      | decreases due to the shared-memory resources that Pure OpenMPI implemen-                                 |     |

|      | tation can not manage it and moreover kernel scheduler is not optimized for                              |     |

|      | this execution model, However on logical cores the trend is almost linear.                               | 119 |

|      |                                                                                                          |     |

## List of Tables

| 2.1  | Most influential and well-known dataflow architectures proposed in last four decades                                                                                                                                                                                                                                                                                                                     | 8  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | The status of the benchmarks that have been developed for the baseline study, software simulation and hardware implementation, N stands for Node and C stands for Cores.                                                                                                                                                                                                                                 | 24 |

| 3.2  | The hardware specification of platforms used in this experiment.                                                                                                                                                                                                                                                                                                                                         | 24 |

| 3.3  | The configurations of the experiment that has been done on <b>Lab146</b>                                                                                                                                                                                                                                                                                                                                 | 26 |

| 3.4  | The configurations of the experiment that has been done on <b>TFX2</b> a Single Multi-core Machine.                                                                                                                                                                                                                                                                                                      | 26 |

| 3.5  | The configurations of the experiment that has been done on <b>TFX3</b> a Single Multi-core Machine.                                                                                                                                                                                                                                                                                                      | 26 |

| 3.6  | The sequential version of Recursive Fibonacci on three platforms TFX2, Lab146 and COTSon simulator.                                                                                                                                                                                                                                                                                                      | 30 |

| 3.7  | The Recursive Fibonacci on platform TFX2 with Cilk programming model                                                                                                                                                                                                                                                                                                                                     | 31 |

| 3.8  | The Recursive Fibonacci on platform TFX2 with MPICH programming model.                                                                                                                                                                                                                                                                                                                                   | 31 |

| 3.9  | The Multi-core experiment execution time for some selected indexes of RFIB<br>on TFX2 machine is presented. In this experiment, the DF-Thread, MPICH<br>and cilk are listed. Note that the execution time is normalized based on the<br>clock frequency and reported value is the average value of 10 repetitions in<br>the loop and is in milliseconds (ms).                                            | 35 |

| 3.10 | The Multi-node experiment execution time for some selected indexes of RFIB<br>on LAB146 machine is presented. In this experiment, the DF-Thread, MPICH<br>and cilk are listed. Note that the execution time is normalized based on the<br>clock frequency and reported value is the average value of 10 repetitions in<br>the loop and is in milliseconds (ms). Each node in this experiment has 1 Core. | 35 |

| 3.11 | The sequential version of Blocked Matrix Multiplication on three platforms TFX2, Lab146 and COTSon simulator.                                                                                                                                                                                                                                                                                            | 39 |

| 3.12 | The Blocked Matrix Multiplication experiment on platform TFX2 with Cilk programming model, here we consider BLOCK size equal to 8 to set the granularity.                                                                                                                                                                                                                                                | 40 |

| 3.13 | The Multi-core experiment execution time for some selected indexes of BMM on TFX2 machine is presented. In this experiment, the DF-Thread, MPICH and cilk are listed. Note that the execution time is normalized based on the clock frequency and reported value is the average value of 10 repetitions in the loop and is in milliseconds (ms) and the BLOCKSZ is equal to 8                            | 43 |

| 3.14 | The Multi-node experiment execution time for some selected indexes of BMM         |    |

|------|-----------------------------------------------------------------------------------|----|

|      | on TFX2 machine is presented. In this experiment, the DF-Thread, MPICH            |    |

|      | and cilk are listed. Note that the execution time is normalized based on the      |    |

|      | clock frequency and reported value is the average value of 10 repetitions in      |    |

|      | the loop and is in milliseconds (ms). Each node in this experiment has 1 Core     |    |

|      | and the BLOCKSZ is equal to 8                                                     | 43 |

| 3.15 | The sequential version of Blocked Cholesky on three platforms TFX2, Lab146        |    |

|      | and COTSon simulator                                                              | 45 |

| 3.16 | The Blocked Cholesky experiment on platform TFX2 with Cilk programming            |    |

|      | model, here we consider BLOCK size equal to 4 to set the granularity              | 45 |

| 3.17 | The Blocked Cholesky experiment on platform TFX2 with MPI programming             |    |

|      | model, here we consider tile size 4 to set the granularity.                       | 48 |

| 3.18 | The sequential version of Histogram on three platforms TFX2, Lab146 and           |    |

|      | COTSon simulator. We consider "bin" size equal to 4 for this measurement          | 49 |

| 3.19 | The Histogram experiment on platform TFX2 with Cilk programming model,            |    |

|      | here we consider "bin"" size equal to 4                                           | 49 |

| 3.20 | The Histogram experiment on platform TFX2 with MPI programming model,             |    |

| 0.20 | here we consider "bin"" size equal to 4                                           | 49 |

|      |                                                                                   |    |

| 4.1  | DF-Threads function definitions [65]                                              | 55 |

| 4.2  | The function name and its corresponding frame pointer address that are shown in   |    |

|      | Fig.4.4 (same as in objdump tool).                                                | 59 |

| 4.3  | Comparing lightweight DRT with other tools for developing dataflow codes and the  |    |

|      | related architectures. As we can see DRT, is using only 300 lines of C code.      | 61 |

| 5.1  | The cloud service cost based on Amazon cloud cost calculator for FPGA f1          |    |

|      | instance cloud servers.                                                           | 65 |

| 5.2  | The cloud service cost based on Amazon cloud cost calculator for CPU instance     |    |

| 0.2  | cloud servers.                                                                    | 65 |

| 5.3  | Brief overview of the most related recent studies on FPGA accelerators and        | 00 |

| 0.0  | their features compared to this work.                                             | 68 |

| 5.4  | Most recent and well-known graph partitioning suitable for FPGA implementation.   | 70 |

| 5.5  | The XACC xilinx server used to evaluate the real implementation.                  | 78 |

| 5.6  | The alveo U250 resource utilization in this experiment.                           | 78 |

| 5.7  | The performance model report, which has been calculated based on the bottlenecks  | 70 |

| 5.7  | like PCIe Rate, Computation time, Communication time, etc. Here the number of SLR |    |

|      | *                                                                                 | 79 |

| EO   | regions used is equal to 1.                                                       | 19 |

| 5.8  | The datasets for evaluating our proposed study. We choose them based on the size  | 70 |

| 5.0  | and the structure of the datasets to be comparable with other works.              | 79 |

| 5.9  | The evaluation of the hardware implementation of the GridGraph algorithm on CPU   | 00 |

|      | and FPGA platform                                                                 | 80 |

| 6.1  | Summarized number of different operations in DPG                                  | 88 |

| 6.2  | Experiment Result for our proposed FFT Algorithm                                  | 89 |

|      | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                           |    |

A.1 The configurations of the experiment that has been done on **TFX3** a Single Multi-core Machine. 118

# List of Listings

| 3.1         | Recursive Fibonacci function code    29                                                        |

|-------------|------------------------------------------------------------------------------------------------|

| 3.2         | Recursive Fibonacci function code using Cilk programming model 30                              |

| 3.3         | The worker function of the Recursive Fibonacci function code using MPI pro-                    |

|             | gramming model                                                                                 |

| 3.4         | The root function of the Recursive Fibonacci function code using MPI program-                  |

|             | ming model                                                                                     |

| 3.5         | BMM using cilk programming model function code                                                 |

| 3.6         | BMM using MPI programming model function code                                                  |

| 3.7         | Blocked Cholesky sequential version function code    46                                        |

| 3.8         | Blocked Cholesky using Cilk programming model function code 47                                 |

| 3.9         | Histogram sequential version function code    48                                               |

| 3.10        | Histogram with Cilk programming model function code 50                                         |

| 3.11        | Histogram with MPI programming model function code 51                                          |

| 5.1         | The function declaration of creating aligned vectors                                           |

| 5.2         | The OpenCL commands used to create buffers between host and kernel 74                          |

| 5.3         | The OpenCL commands to run the kernel using appropirate arguments and                          |

|             | pointing to created buffers in Listing 5.2                                                     |

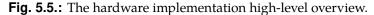

| 5.4         | The kernel function declaration.    77                                                         |

| 5.5         | The multi kernel configuration that enables running multiple instances of the                  |

|             | kernel in parallel from the host program                                                       |

| A.1         | How to compile and set environment variables for mpiP profiling tool 113                       |

| A.2         | The command specifications to specify the region of interest to profile with mpiP114           |

| A.3         | The output of profiling the OpenMPI benchmark with mpiP from LLNL repos-                       |

|             | itory. The results show the MPI overhead and UsrTime compared to the overall                   |

|             | execution time                                                                                 |

| A.4         | The aggregate collective report from mpiP profiling, matrix size 2000 and number of workers 15 |

| A.5         | The mpiP output log and how to calculate manually the runtime, this runtime                    |

| <b>A</b> .5 | time is not a part of the mpiP output log                                                      |

| A.6         | The script to iterate the experiment of a loop and collect the numbers, producing              |

| 1 1.0       | a suitable csv file that can be used for reports                                               |

| A.7         | The script to fetch numbers from a generated csv file and plot it using GNUPLOT120             |

|             |                                                                                                |

| A.8 | The GNUPLOT script uses to create graphs using the csv file output. The user      |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | should take care of the name of the csv file and other decorations such as title, |    |

|     | fonts, etc                                                                        | 21 |

## List of Abbreviations

| AI         | Artificial Intelligence.                 |

|------------|------------------------------------------|

| API        | Application Programming Interface.       |

| ASIC       | Application Specific Integrated Circuit. |

| AXI        | Advanced eXtendable Interface.           |

| AXIOM      | Agile eXtensible Input Output Module.    |

| BMM        | Blocked Matrix Multiplication.           |

| CPU        | Central Processing Unit.                 |

| DSP        | Digital Signal Processor.                |

| DSM        | Distributed Shared Memory.               |

| DSE        | Design Space Exploration.                |

| DFG        | Dataflow Graph.                          |

| DF-Threads | Dataflow-Threads.                        |

| DLP        | Data Level Parallelsim.                  |

| HBM        | High Bandwidth Memory.                   |

| HLS        | High Level Synthesis.                    |

| ILP        | Instruction Level Parallelism.           |

| ISA        | Instruction Set Architecture.            |

| IP         | Intellectual Property.                   |

| GPU        | Graphic Processing Unit.                 |

| GCC        | Gnu Compiler Collection.                 |

| FPGA       | Field Programmable Gate Array.           |

| FP         | Frame Pointer.                           |

| FIFO       | First-In, First-Out.                     |

| FFT        | Fast Fourier Transform.                  |

| LUT  | Look-up Table.                       |

|------|--------------------------------------|

| NIC  | Network Interface Card.              |

| OS   | Operating System.                    |

| PL   | Programmable Logic.                  |

| PS   | Processing System.                   |

| RAM  | Random Access Memory.                |

| RISC | Reduced Instruction Set Computer.    |

| RDMA | Remote Direct Memory Access.         |

| RFIB | Recursive Fibonacci.                 |

| ROI  | Region of Interest.                  |

| SC   | Synchronization Count.               |

| SSSP | Single Source Shortest Path.         |

| SoC  | System on Chip.                      |

| SpMV | Sparse Matrix-Vector Multiplication. |

| SPI  | Serial Peripheral Interface.         |

| TLP  | Thread Level Parallelism.            |

| WCC  | Weakly Connected Components.         |

|      |                                      |

### Abstract

This thesis mainly focuses on state-of-the-art challenges of distributed execution models and research the system support for artificial intelligence and high performance computing applications. In this context, we focus on investigating in detail about co-designing the Dataflow-Threads execution model [61]. Moreover, to facilitate support, development, and debug the Dataflow-Threads execution model, we introduced DRT; a lightweight Dataflow runtime [68]. DRT has been written in portable C code (tested with the GNU C compiler), and it is open-source. It can be used on real machines based on architectures like x86, AArch, RISC-V ISA.

Furthermore, we consider major problematic applications in the domain of the Artificial Intelligence (AI) and High Performance Computing (HPC) and address the main challenges and bottlenecks to extend our dataflow runtime. To do this, we used widely known benchmarks to stress the capabilities of the DF-Threads execution model and its evaluation against other parallel programming models. We choose Blocked Matrix Multiplication and Recursive Fibonacci. Matrix multiplication is one of the main kernels of AI and HPC Applications. Plus, Recursive Fibonacci is a simple benchmark which creates enormous number of threads and processes and stress the entire execution model.

In this thesis, we are mainly interested in heterogeneous platforms. A heterogeneous platform is a hardware device that contains a range of computing components, such as multicore CPUs, GPU, or FPGAs. Their capabilities have provided many features for researchers to use this kind of structure in their state-of-the-art works. Heterogeneous systems are flexible, cost-efficient, and well-supported by communities. Our work focuses mainly on CPU+FPGA Heterogeneous systems, mostly a general-purpose CPU (x86 or ARM) within a Unix-based operating system besides an FPGA accelerator. Subsequently, because of a need in our hardware platform structure, we design and fabricate the Gluon board, which uses serial transceivers in Xilinx Ultrascale+ Heterogeneous accelerator and facilitates GTH transceivers in high rate data transfer applications. Gluon boards are modular and can carry up to 18 Gbps on each lane with specific data types and payload sizes. The end-user cost to manufacture the Gluon board is less than 400 euros with enormous capabilities.

Moreover, a real application demonstrates a distributed graph processing application to express the distributed computing execution model and further extend our execution model to cover the real-world application like Graph Processing in large scale. In the first step, we provided a comprehensive baseline, designed and proposed a large scale distributed graph processing application and evaluated it within the PageRank algorithm using well-known datasets. We show how graph partitioning combined with a multi-FPGA architecture leads to higher performance without limitation on the size of the graph, even when the graph has trillions of vertices. Our performance analysis, in the case of PageRank, forecasts performance improvement of up to 20 times and a cost-normalized improvement of up to 12 times when comparing the proposed approach on one Xilinx Alveo U250 FPGA accelerator against a state-of-the-art baseline graph processing software implementation on a Intel Xeon server CPU with a 40-core processor at 2.50 GHz.

### Introduction

99

What is essential is invisible to the eye.

— Antoine de Saint-Exupery (Writer, 1900-1944)

Reconfigurable computing is an emerging field that has rapidly grown during recent years, and numerous research areas increasingly deal with reconfigurable hardware and their architecture to implement computations. From wearable gadgets to datacenters, reconfigurable hardware is employed on a large scale and the trend of using reconfigurable hardware grows everyday in all aspects. Different technology of reconfigurable hardware such as Field-Programmable Gate Arrays (FPGAs), Digital Signal Processors (DSPs), and Graphics Processing Units (GPUs) could successfully mitigate the bottlenecks of the ASIC hardware while they had the majority of the market before. Basically, ASIC hardware accelerators were effective, however, they are fraught with challenges. The major problem with ASIC is that as algorithms change rapidly, hardware must be re-designed and reverified, which is costly in development time and time-to-market. Consequently, algorithm innovation becomes more difficult without access to a flexible hardware. Furthermore, fixed accelerators cannot be shared across applications, making them more costly in the fabrication process. Ideally, a hardware that is capable of executing compute-intensive algorithms at high performance with much lower power than programmable architectures is required while remaining broadly applicable and adaptable. This work, in collaboration with my research group, mostly focus on FPGA as a suitable hardware to adapt and reconfigure effectively our new concepts and build the new prototype. FPGA has several advantages to DSP and GPU for instance FPGA has more power efficiency than GPU [161]. In addition to power consumption, FPGA can cover a broad range of applications while GPU is mostly used for vector processing and even though the development time with GPU is less than FPGA. GPU is more power hungry and likely is avoided in datacenters and compute intensive applications when power and money has the crucial role, whereas, FPGA offer some distinct advantages like low latency when it comes to the networking applications. Finally, The most important advantage of FPGA regards irregular algorithms like Graph Processing is that FPGA has sequential data access and can mitigate the irregular access to the memory whilst GPU and CPU have conventional random memory access architecture. We will discuss this more in details later in the next chapters.

### 1.1 Motivation and contribution

Our group Ph.D. research line expresses the state-of-the-art challenges of distributed execution models and research the system support for high performance computing applications. In this context, our research group focus is on Dataflow-Threads and its execution model [67].

The contributions of this thesis are as follows:

- 1) Providing comprehensive literature review to understand how Dataflow-Threads can be distinguished from other recent studies.

- 2) Providing a solid baseline and benchmark suite to compare our Dataflow-Threads execution model with other parallel programming models, such as OpenMPI and Cilk. A unique algorithm for all mentioned programming models is developed and unique methodology is performed to collect the results. Moreover, this work investigates in detail to show which bottleneck has been faced within each experiment.

- 3) Providing a case study of the Distributed Graph processing on the Multi-FPGA platform. This is a collaboration between two research groups to exploit the potential of distributed reconfigurable platforms within the real-world application. This work mainly studied PageRank and compared the performance model within actual implementation and baseline studies.

### 1.2 Thesis Structure

The structure of this thesis is as follows:

### Chapter 1

This chapter is the introductory discussion about the Program Execution Models (PXM), and more specifically, I discuss Dataflow Execution Models and the recent works in the literature. I briefly point to the most important research and their contributions by their category. This chapter introduces the different categories of Dataflow Abstraction and their Execution Models. Then, a review of the most challenging and significant works to mitigate any failure or bottleneck within this Abstraction Model will be addresses. This study shortly introduce previous works in our laboratory, which have been done previously and present their contributions briefly.

The aim of the chapter is to answer the following question:

**Q.** There have been many studies and investigations in Dataflow architectures since early 70's, The question is what is the status of the Dataflow Execution Models nowadays? How much are they successful to surpassing conventional methods?

### Chapter 2

This chapter reviews the most recent literature studies based on Dataflow Execution Models. Moreover, I concisely point to some recent studies more similar to our work. In this chapter, I differentiate our work from other studies, and I demonstrate the variety of the contributions and their impact on the Dataflow Computing subject, and finally show a landscape of state-of-art implementations focusing on Dataflow Execution Models.

The aim of the chapter is to answer the following question:

**Q.** This thesis focuses on Hybrid Dataflow Execution Model, The question is based on the literature, what are challenges, bottlenecks and approaches recent studies have addressed? and finally, what is the main features of a fine-grained dataflow execution model?

In particular, I discuss the selected studies implementation and their issues and I compare them with ours and other related ones.

### Chapter 3

This chapter discusses the need for a strong baseline for our research line. Many studies in the literature discuss the bottlenecks and propose new methods in parallel programming. However, a strong baseline in which all the aspects that have been studied carefully is missing. In particular, parallel computing is a challenging concept, and many methodologies are proposed to program, calculate and measure the metrics for the specific computation. This work investigates several essential benchmarks in parallel programming and shows essential aspects of a baseline and measurements. This work compares well-known parallel programming models like OpenMPI, OpenMP and Cilk and discuss the lessons learned during the baseline experiments.

The aim of the chapter is to answer the following question:

**Q.** The question is based on the proposed methodology, how we can have a strong baseline to evaluate our execution model and in particular our Dataflow Thread execution model?

### Chapter 4

This chapter, introduces the Dataflow Thread Runtime (DRT). DRT is a lightweight runtime to develop and debug dataflow based examples to be targeted by a future compiler for the dataflow programs. The key point of DRT is that most of the dataflow runtimes do not provide test and debug feature for developers to follow the execution model of the dataflow program. DRT enables such feature for developers and has potential to be a backend of the compiler in our workflow.

The aim of the chapter is to answer the following question:

**Q.** The question is as we investigated in the literature, how we can have a lightweight runtime to test and debug Dataflow Thread programs? DRT is the solution to answer this need.

Chapter 5

In this chapter with the collaboration of my reseach group express a *Big Scale Distributed Graph Processing* as a case study to fullfill the "borse Pegaso ciclo 34" obligatory activity abroad the country. The materials in this chapter are a collaboration between the University of Siena (Smart Computing Program) and "Custom Computing Research Group at Imperial College London". In this period, I defined a project based on the a Reconfigurable Graph Processing Model that addresses the current challenges and needs to cover both groups Ph.D. goals. This study can bring possibilities to the user and have many advantages despite a few current ones in the literature and I am progressing with the implementation. The aim of the chapter is to answer the following question:

**Q.** The question is can the distributed graph processing on multi-FPGA platform be a good solution for large scake graph processing and can be effectively compared with CPU based graph processing solutions?

### Chapter 6

At the beginning of my Ph.D. studies, I had this chance to collaborate with Dr. Lorenzo Verdoscia at the Institute for High Performance Computing and Networking (CNR). Our collaborating concluded with an Dataflow Approach to accelerating FFT application and we got the **Best Paper Award** of the 8th Mediterranean Conference on Embedded Computing (MECO) in Budva, Montenegro, 2019.

# **Q.** The question is can we provide a fast and reliable methodology based on Dataflow concepts to process FFT as a widely used kernel in many applications?

### Chapter 7

This chapter presents *Individual Research Activity* that have been carried out during the Ph.D. program. The studies presented in this chapter are collaboration between myself with other colleagues. I present the Gluon board in this chapter. GLUON board is the modified and enhanced version of the TEBT0808 board from Trenz Company [69], which with the new design is able to power up the FPGA module with unix-based operating system. GLUON enables serial transceivers in Xilinx Ultra-scale+ structure and facilitates using GTH transceivers in high rate data transfer applications.

#### Chapter 8

This chapter concludes the thesis. In this chapter we summarize the most important findings from this work, the main achievements and what has been undergoing will be pointed in three years of Ph.D. program. Of course the time limitation does not allow to dig into all aspect of the theoretical and implementation of the study. I discuss in this chapter what is left to be completed and what is the overseen studies to addresses in the future works.

### **Related works**

*The more you know, the more you realize you know nothing.*

— Socrates, Philosopher, 400 BC

This chapter contains two major parts. In the first part, I introduce Dataflow Architecture and its Execution model. I shortly introduce our concept of Dataflow-Threads and its potential to be deployed on reconfigurable architecture. To this end, we demonstrate our concept, the challenges and bottlenecks, and the achievements so far. The achievements and improvements of our research line in the recent years and the similar state-of-the-art studies will be addressed.

The dataflow model represents a revolutionary alternative to the control flow (also known as the von Neumann) model since the execution is driven only by the availability of operands. A pure dataflow execution model has no program counter (PC) and global memory, the two major elements of the von Neumann model that become bottlenecks of its performance [138]. In dataflow computing, only limitation of parallelism is the data dependences between instructions in the application program [152]. However, it is well investigated that data driven feature of dataflow computers have the potential for exploiting all the parallelism available in a program [44, 43, 10, 12, 11].

In conventional von Neumann machines, due to the dependence of the commands from the PC, which also fetches load and write commands, there may be delays in the entire program's execution, whereas, in a dataflow machine, the dependencies and instructions are inside the processor already. The procedure to see all these dependencies is called *Dataflow Graph* and dataflow machines use dataflow graphs as their machine language. A dataflow graph (DFG) comprises arcs and nodes, with the nodes representing locations where variables are assigned or used and the arcs representing the link between the places where a variable is allocated and the places where the assigned value is used later. Based on the graph, the independent instructions can now be executed first, followed by instructions whose operands are available later. Unlike conventional machine languages, dataflow graphs specify only a partial order for the instruction execution and thus provide opportunities for parallel and pipelined execution at the Instruction level.

In this chapter, I discuss the related studies in terms of expressing most influential works and their approaches to mitigate the deficiency and enhance the strength of dataflow execution models. There are several category field of studies that I can discuss separately towards them in this chapter. The categories are described as follows:

1) Dataflow Architecture Discussion

- 2) Fine-grained Parallelism Approaches in Dataflow Architecture

- 3) Dataflow Runtime Libraries

- 4) Dataflow Execution Models using Hardware Accelerator

### 2.1 Dataflow architecture

So far we had a brief understanding of what is a dataflow architecture. There have been several efforts to build a dataflow hardware. In Fig. 2.1, the dataflow inspired models that have been studied or even built, and used for several years has been depicted. These works that are mentioned here are the most well-known studies, some works have been ommitted for the sake of readability of the picture. Our work is based on Teraflux [67] and DF-Threads execution model on Heterogeneous platform like AXIOM [63] that can be seen in the Fig. 2.1.

Beside these mainline researches, there have been many studies about dataflow architecture with different research subjects. Some earlier studies try to introduce and build the dataflow hardware [117, 76], some other ones try to introduce the dataflow languages and their compiler [168], and some other research are based on developing dataflow execution models and their runtime libraries [157, 61, 5, 60, 102, 50]. An increasing number of studies have introduced their application based study based on dataflow computing. These works cover a wide range of domains such as power efficiency [174, 70, 22], high performance computing [52, 55, 133], computing scientific algorithms [159, 158], artificial intelligence [169, 101] and accelerators for general purpose applications [163].

### 2.2 Taxonomy of dataflow execution models

What was mentioned already was a brief discussion about the dataflow architecture and the studies since 1970. This section presents a taxonomy of dataflow architecture, programming model, and execution models. There are several efforts in the literature to provide a comprehensive study about dataflow [173, 152, 155, 21, 97, 138]. However, several items are missing in these works, which are as follows. **First**, they did not cover the recent studies and most covered works have been done between 70's and 90's. **Second**, it is not obvious where and how dataflow is going forward and how dataflow can be used in the next generation of computers.

Table 2.1 shows a survey of dataflow architecture based on the state-of-the-art. In this Table, we show the most influential works and thier taxonomies and importants feature to point out. In this table, the level of parallelism categorizes in three levels, **ILP** (*Instruction Level Parallelism*), **DLP** (*Data Level Parallelism*), and **TLP** (*Task level Parallelism*).

Fig. 2.1.: The most influential dataflow inspired and non-dataflow architectures and their timeline.

I aim to find the most bold features and the roadmap of these works. Moreover, I would like to show what is the possible future of the dataflow architecture. More specifically, what is the potential and where does the dataflow architecture go in the next years.

### Static Dataflow

Dennis and Misunas [44] proposed the Static Dataflow model of computation to design, evaluate, and implement computations that work on endless streams of data. A static dataflow model is a directed graph of computational actors with FIFO channels connecting them. The amount of tokens consumed and created by an actor must be fixed and prespecified in the static dataflow semantics. This ensures that crucial model features such as deadlock-free and memory-bounded infinite computation, throughput, latency, and execution schedule can be determined. There are other several efforts based on static dataflow model such as HDFM [154], NEC [146], DDM1 [41]. Although static dataflow was a basis of many efforts on 70's till 90's, however, there were several fundamental issues with this model. We briefly discuss some issues regarding the static dataflow model,

- There was a mismatch between the model and the implementation, The model requires unbounded FIFO token queues per arc (which represent data dependences among instructions) but the architecture provides storage for one token per arc.

- 2) The architecture does not ensure FIFO order in the reuse of an operand slot.

- 3) The static model does not support the **function calls** and **loops**

- 4) No **Data Structures** is supported in this model. So it was hard to program and exploit the data locality.

### **Tab. 2.1.:** Most influential and well-known dataflow architectures proposed in last four decades.

| Dataflow<br>Architecture | Key Concept                                                                                                                                                                                                                                                                                                                                                                                   | Key Features                                                                                                                                                                                                                                                                                                                                                                                                                                                | Level of<br>Parallelism | Studies<br>References                    | Presenting<br>Year |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------|--------------------|

| Static Dataflow          | In static dataflow, a program is<br>described as a set of operator nodes,<br>called actors, interconnected by a<br>set of data-carrying arcs, called<br>links. Data is passed through this<br>graph in one and only one packet<br>called tokens.                                                                                                                                              | <ol> <li>Too much parallelism.</li> <li>Acknowlegment is needed for each token and makes<br/>the tokens traffic double</li> <li>Asynchronous execution.</li> <li>Order of instruction execution is unpredictable, thus<br/>the execution in uncertain.</li> <li>Loops as a major bottleneck of many programs can<br/>only be parallelized in sequential manner.</li> </ol>                                                                                  | ILP                     | [44, 154, 146, 41, 10,<br>80, 19]        | 1974-1987          |

| Dynamic<br>Dataflow      | In contrast with statis dataflow<br>model, In dynamic dataflow<br>concept, the number of tokens that<br>can be carry data in dataflow graph<br>is unlimited.                                                                                                                                                                                                                                  | <ol> <li>Loops can be parallelized, each iteration as<br/>independent subgraph in the whole dataflow graph<br/>model.</li> <li>Suitable for stream computing models.</li> <li>Introduce the data structure to dataflow architecture.</li> <li>Not efficient in terms of memory, since there is a huge<br/>need to store abundant number of tokens.</li> </ol>                                                                                               | TLP                     | [11, 138, 156, 124]                      | 1987-1993          |

| Hybrid Dataflow          | Introduced in the late 80's and<br>significant studies have been done<br>quickly for almost two decades.<br>There are two types of Hybrid<br>model. Dataflow/Control flow and<br>Control flow/Dataflow. The former<br>got most attention and has the<br>benefit of scheduling based on<br>dataflow semantic, whilst each<br>basic block inside executes<br>sequential control flow computing. | <ol> <li>Combine the dataflow and von-Neumann models of<br/>computation can mitigate the deficiency of both<br/>models.</li> <li>Control the granularity while being substantially<br/>power efficient.</li> <li>More program developing friendly than others.</li> </ol>                                                                                                                                                                                   | TLP, ILP                | [149, 126, 19, 164, 96,<br>67]           | 1982-2004          |

| Threaded<br>Dataflow     | This model is also known as<br>"Data-Driven Multithreading". The<br>key factor of this model is to<br>intorduce the Task Synchronization<br>Unit (TSU) to the dataflow<br>semantics.                                                                                                                                                                                                          | <ol> <li>A "thread of instructions" is issued consecutively by<br/>the matching unit without matching further tokens<br/>except for the first instruction of the thread.</li> <li>Data passed between instructions of the same thread<br/>is stored in registers instead of written back to<br/>memory.</li> <li>The cycle-by-cycle consecutive instruction interleaving<br/>of threads is same as von-Neumann control flow<br/>execution model.</li> </ol> | TLP, ILP                | [72, 151, 117, 135,<br>140, 36, 129, 79] | 1988-1996          |

| Spatial Dataflow         | In a producer/consumer fashion,<br>spatial dataflow maps directly a<br>Dataflow Graph (DFG) on<br>resources available on a hardware<br>(PEs). Therefore, provide the<br>parallelism to compute program on<br>a core in space not in time.                                                                                                                                                     | <ol> <li>There is no need for instructions because the<br/>hardware itself represents the computation.</li> <li>There is also no need for memory decode logic,<br/>branch prediction or out of order scheduling.</li> <li>Ease of programming development.</li> <li>Suitable for many cases specifically streaming<br/>application.</li> </ol>                                                                                                              | TLP                     | [105, 29, 28]                            | 2006-2015          |

| Stream Dataflow          | The concept is to set the operations<br>(kernel functions) that applied to<br>each element in a stream given a<br>sequence of data (a stream). Stream<br>dataflow take advantage of<br>integrating stream programming<br>language with dataflow execution<br>model concepts.                                                                                                                  | <ol> <li>Is based on streaming memory access and reuse<br/>patterns</li> <li>High concurrancy beside low power consumption and<br/>low overhead</li> <li>less available hardware built so far.</li> </ol>                                                                                                                                                                                                                                                   | ILP                     | [110, 165, 120, 89]                      | 2015-2019          |

5) There are **too much parallelism** generated by the architecture but there is no way to schedule them effectively to leverage this level of parallelism.

These limitations manke researchers to investigate more about the fundamental problems regard static dataflow. In TTDA [10] and HPS [80] in the 80's, researchers tried to mitigate the static dataflow issues by adding more synchronization and resource managing ability to the tokens, while preserving sequential ISA semantics. These efforts brought the idea of starting another branch of the dataflow architecture which represented as *Dynamic Dataflow*.

### **Dynamic Dataflow**

Once loop iterations and subprogram invocations could run in parallel, a dataflow machine's speed improves dramatically. To achieve this, each loop iteration or subprogram invocation should be executed as a separate instance of a re-entrant subgraph. This replication, on the other hand, is simply theoretical. Only one copy of any dataflow graph is actually kept in memory in a real implementation. Each token has a tag consisting of the address of the instruction for which the particular data value is destined and other information defining the computational context in which that data is to be used. This concept was led to build the hardwares based on Dynamic Dataflow concepts such as MIT Tagged-Token Dataflow Architecture [11] and Monsoon [117].

### **Spatial Dataflow**

Spatial architecture is a type of accelerator that uses direct connection between a number of very basic processing engines (PEs) to utilise significant computational parallelism . Different algorithms can be built or coded into them, which are then mapped onto the PEs utilising specific dataflows. Spatial architectures, as opposed to SIMD/SIMT designs, are better suited to applications with producer-consumer interactions or that may benefit from efficient data exchange throughout an area of PEs. One example of such design is Maxeler Dataflow Engines [105]. Data is streamed from memory onto a chip on a dataflow engine (DFE), where it goes directly from one functional unit to another without being written to off-chip memory until the entire operation is completed. A control flow core executes operations at different points in time on the same functional unit "computing in time", whereas a dataflow core does computation on a chip spatially "computing in space". Instructions are not required in a DFE because the DFE itself represents the computation. As a result, no memory decode logic, branch prediction, or out of order scheduling is required, allowing the chip to devote all of its resources to computation [118].

Another work that leverage spatial dataflow is Eyeriss [31]. Eyeriss is made up of a collection of processing elements (PEs), each of which contains logic to compute multiplyand-accumulate (MAC) and local scratch pad (SPad) memory to take advantage of data reuse, as well as global buffers (GLBs), which provide an extra level of memory hierarchy between the PEs and the off-chip DRAM. There are two version of Eyeriss project. One major difference between Eyeriss v1 and Eyeriss v2 is that the latter uses two-level memory hierarchy [29].

#### Hybrid Dataflow

There have been two basic models in computer architectures: (1) the *von Neumann se-quential* control model; and (2) the *dataflow data-driven* computing model. The parallel architectures based on the von Neumann model aim to exploit coarse-grain parallelism, while the traditional dataflow architecture model was conceptualized to handle fine-grain parallelism. For the past years, researchers have debated which model is a "more efficient" basis for future large-scale parallel computer systems [58].

One of the very first hardwares based on hybrid dataflow was MDFA [57]. In MDFA work clearly the concept of integrating von Neumann model of computing with dataflow computing model is implemented and discussed. At that moment, there were other proposed methods called "macro-dataflow", which was different from the concept of nowadays so called "hybrid dataflow".

There is not a clear discussion that when and how the integration of "von Neumann sequential" execution model plus "dataflow semantics" named hybrid dataflow but there are many works that discussed and studied this concept and produced many great works in this context such as [67, 88, 102, 117, 111]. In these mentioned work, explicitly the potential of integrating control flow computing model plus dataflow execution model is discussed and hardware prototypes have been created moslty using reconfigurable devices such as FPGA. There are imbiguity of using integration of control flow model with dataflow in hybrid dataflow computing, we must point out that, in particular we are focusing on **Dataflow-> Control flow** execution model. This concept employs basic blocks of containing control flow program, scheduled based on the dataflow execution paradigm. The basic block is a set of sequential instructions, where data is passed between instructions using register or memory as a usual conventional method to execute control flow programs.

#### Threaded Dataflow

In some previous studies, Hybrid Dataflow and Threaded Dataflow are categorized in one seed. However, they are slightly different. Threaded Dataflow is a dataflow modification approach in which instructions from specific instruction streams are executed in sequential machine cycles. Whereas in Hybrid Dataflow this means *threaded basic blocks* are being executed in a dataflow way). EM-4 [135] and its updated version EM-X [90], and Monsoon [117] are well-known successful projects based on Threaded Dataflow. The implementation of an effective *synchronisation mechanism* is the key design problem in all threaded dataflow machines. Direct matching is a synchronisation mechanism that does not require the use of associative mechanisms [153]. In [145] authors introduced an implementation of threaded dataflow model on FPGA. This work is the development of a Thread Synchronization Unit (TSU) on FPGA, a hardware unit that enables thread execution on a chip multiprocessor utilising dataflow rules. Threads are executed depending on data availability, which means that a thread is launched only if its input data is available. This execution model is known as the non-blocking Data-Driven Multithreading model. Other efforts, such as [175], have exploited this approach to build an recursively organized data-driven machine, RWC-1 is capable of automatically and dynamically allocating concurrent tasks to the available hardware units.

#### Stream Dataflow