# Failure Prevention in DC–DC Converters: Theoretical Approach and Experimental Application on a Zeta Converter

Marco Bindi<sup>®</sup>, *Graduate Student Member, IEEE*, Fabio Corti<sup>®</sup>, *Member, IEEE*, Francesco Grasso<sup>®</sup>, *Member, IEEE*, Antonio Luchetta<sup>®</sup>, *Member, IEEE*, Stefano Manetti<sup>®</sup>, *Member, IEEE*, Maria Cristina Piccirilli<sup>®</sup>, *Member, IEEE*, and Alberto Reatti<sup>®</sup>, *Member, IEEE*

Abstract-In this article, we propose a monitoring procedure based on a multilayer neural network with multivalued neurons (MLMVN) capable of preventing catastrophic failures of dc-dc converters. The neural classifier allows both the detection of any malfunction and its localization. Thanks to the low computational complexity, the proposed method operates online, estimating the deviations of the passive components from their nominal values: this allows control strategies to be promptly adopted and operation of the dc-dc converter to be kept in high efficiency and reliability conditions. Since measuring the voltage and current on each component increases the complexity of the system, a testability analysis is proposed with the aim of identifying the minimum number of measurements needed to distinguish the classes of failure. To make the testability phase easier and more intuitive, a graphical representation is proposed. As a case study, prognostic analysis has been applied to prevent catastrophic failures in a synchronous Zeta converter. Several fault conditions have been analyzed through simulations and experimental tests. The obtained results confirm the ability of the proposed method to prevent failures and, also, show that the application of MLMVN results in a better performance than classic solutions available in the literature, such as support vector machine.

*Index Terms*—DC–DC converter, fault diagnosis, multilayer neural network with multivalued neurons (MLMVN), prognostic analysis, support vector machine (SVM), Zeta converter.

## I. INTRODUCTION

**P**OWER converters have a large application in fields, such as automotive, renewable energies, aircraft, smart grid, and

Manuscript received 1 October 2021; revised 19 January 2022; accepted 11 February 2022. Date of publication 1 March 2022; date of current version 22 August 2022. (*Corresponding author: Marco Bindi.*)

Marco Bindi, Francesco Grasso, Antonio Luchetta, Stefano Manetti, Maria Cristina Piccirilli, and Alberto Reatti are with the Department of Information Engineering, University of Florence, 50139 Florence, Italy (e-mail: m.bindi@unifi.it; francesco.grasso@unifi.it; antonio.luchetta@ unifi.it; stefano.manetti@unifi.it; mariacristina.piccirilli@unifi.it; alberto. reatti@unifi.it).

Fabio Corti is with the Department of Industrial Engineering, University of Perugia, 06125 Perugia, Italy (e-mail: fabio.corti@unipg.it).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TIE.2022.3153827.

Digital Object Identifier 10.1109/TIE.2022.3153827

other industrial and consumer applications. These circuits are the most vulnerable parts of integrated power systems [1]–[3] and their failures often produce damages or downtimes, which requires costly maintenance procedures.

To avoid these problems, redundancy has been historically adopted to increase the reliability of the system these converters are utilized in. Although this solution allows for greater failuretolerance capability, it also increases the cost and size of power converters.

To overcome this limitation, the design for reliability approach has been developed in recent years, which consists in explicitly considering reliability during the design process. This approach, together with continuous monitoring of dc-dc converters, allows an increase in the expected lifetime. The monitoring can be implemented through different approaches, such as model-based, signal-based, or knowledge-based techniques [4], [5]. The recent diffusion of artificial intelligence in the industrial sector has led to the development of monitoring systems based on neural networks [6] and other machine learning algorithms [7], focusing on the data-driven approach. Most of these techniques focus on power semiconductors, such as MOSFETs and IGBTs [8], [9]. Usually, the monitored parameter is the device's conduction resistance, which increases with aging [10], [11]. As shown in [12], the conduction resistance is approximately constant when the semiconductor operates in healthy conditions, while it exponentially increases just before its failure. Consequently, the failure of a switching semiconductor is easily detected because it quickly affects the power converter operation. This behavior justifies the large number of papers related to the use of redundancy of semiconductor components to make the systems fault tolerant, usually connecting modules in parallel to guarantee the functioning of the system until the repair, allowing continuity of service [13], [14].

To obtain a monitoring system capable of preventing catastrophic failures in dc–dc converters, it is crucial to consider passive components whose variations from the nominal values represent possible malfunctions and occur over a longer time [15], [16]. Therefore, this article focuses on detecting changes in passive component values using a multilayer neural network with multivalued neurons (MLMVN).

0278-0046 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

930

In the literature, there are some works related to the monitoring of power converters using machine learning algorithms [17], [18]. One of the most critical aspects is the number of measurements required to identify different failure scenarios and the absence of the prevention aspect. In [19], a possible monitoring approach for two different dc–dc power converters is proposed, where a continuous version of an MLMVN is used for the parametric identification of passive components. This neural network is used to solve a regression problem that requires a large number of measurements to identify the exact values of a few elements. In particular, current and voltage measurements are used to obtain the identification of two passive components in a buck and in a boost topology [19].

To overcome these limitations, the prognostic procedure proposed in this article is based on a discrete MLMVN, which allows the detection of malfunctions and the localization of their causes using a small number of voltage measurements. Therefore, the main objectives of the article can be summarized as follows.

- To propose a graphical method for the testability analysis, which facilitates the selection of test points, avoiding ambiguity situations. In fact, variations on different passive components could introduce indistinguishable effects on measured quantities. The testability study determines how many and which measurements are required for the detection and exact localization of malfunctions [20]. Different from the existing testability analysis [21], [22], the proposed graphical representation does not require the extraction of the analytical transfer function. The testability curves obtained with the proposed method are suitable for dc–dc power converters, where different topologies alternate during normal operation and the mathematical approach may not be easily applicable.

- 2) To develop a neural classifier based on multivalued neurons (MVNs). The main theoretical aspects of these neurons are presented in [23], where their continuous and discrete activation functions are introduced. In this article, a three-layer MLMVN is used, and a particular configuration of the hidden and the output layers is proposed. In fact, the neurons belonging to the hidden layer are characterized by a continuous activation function, while the output neurons are discrete and are used in the binary configuration. This means that the discrete classifier presents one output for each passive component and this allows the localization of malfunctions and also reduces recovery times; moreover, it increases the reliability of the converter. During the training phase of the MLMVN, the batch algorithms presented in [24] are used after adapting the error calculation to the structure of the classifier and introducing the "winner takes all" rule.

- 3) To validate experimentally the proposed failure prognosis technique on a Zeta converter.

The rest of this article is organized as follows. Section II shows the main characteristics of the synchronous Zeta converter. Section III presents the most important aspects of the prognostic procedure. Section IV describes the MLMVN setup. Section V presents the main results of the experimental procedure. Finally, Section VI concludes this article.

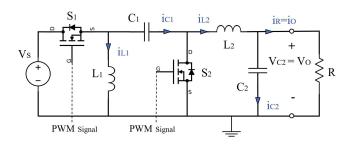

Fig. 1. Topology of Zeta converter.

#### II. ZETA CONVERTER

In recent years, dc–dc conversion has been greatly developed in many sectors of the industrial world, and the Zeta converter has been applied with excellent results in terms of power density and output ripple [25]. Thanks to its simple structure and its ability to operate as a buck–boost converter with a noninverted output, it has been used in many different applications: as an electric vehicle battery charger powered by a photovoltaic (PV) array [26], as a dc motor controller [27], and as grid interface in a standalone dc microgrid [28].

The elementary circuit of the synchronous Zeta converter is shown in Fig. 1.

The circuit results in a fourth-order step-up/step-down converter characterized by two inductors ( $L_1$  and  $L_2$ ) and two capacitors ( $C_1$  and  $C_2$ ). This topology guarantees a noninverted polarity of the output voltage, and this represents one of the most important advantages over other transformerless dc-dc buckboost converters. The pulsewidth modulation (PWM) technique is used to drive MOSFETS  $S_1$  and  $S_2$  at a switching frequency f. Assuming the converter is operated under a continuous conduction mode (CCM), during a switching period T = 1/f, two topologies alternate depending on  $S_1$  state: ON period ( $S_1$  ON and  $S_2$  OFF) and OFF period ( $S_1$  OFF and  $S_2$  ON). The first one, the switch-ON period, lasts  $t_{off} = (1-D)T$ .

During *DT*,  $L_1$  is charged by the input voltage source and  $L_2$  by capacitor  $C_1$ . This means that both inductors are in the charging state and their currents linearly increase. During OFF-mode,  $L_1$  and  $L_2$  discharge through  $C_1$  and the resistive load *R*, respectively.

## A. Dimensioning and Simulation

To develop the prognostic procedure focused on the passive component variations, a Simulink model of the synchronous Zeta converter has been implemented. By using this model, the operation of the circuit in every working condition is verified, and the dataset matrix needed for the training phase of the classification tool is generated. The Simulink-Simscape library is used to achieve this purpose, and common Simulink blocks are introduced to generate the PWM signal driving  $S_1$  and  $S_2$  with opposite phases.

The design procedure shown in [29] has been used. Table I summarizes the nominal values of the converter components, ensuring operation in CCM and a peak-to-peak output ripple lower than 5%.

TABLE I CONVERTER COMPONENTS

| L <sub>1</sub> ( μΗ ) | <i>L</i> <sub>2</sub> ( µH ) | $C_1 (\mu F)$ | $C_2(\mu F)$ | $R(\Omega)$ |

|-----------------------|------------------------------|---------------|--------------|-------------|

| 380                   | 380                          | 1.4           | 1.4          | 10          |

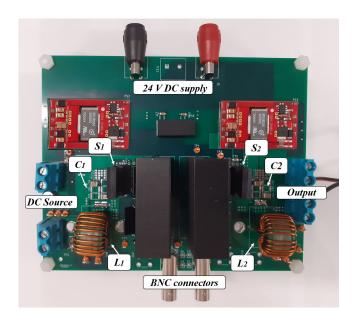

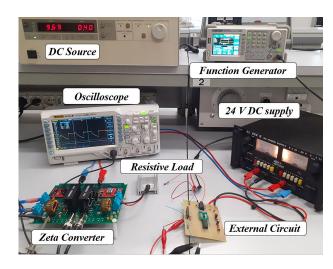

Fig. 2. Experimental prototype of the synchronous Zeta converter.

To derive a monitoring method capable of detecting changes in passive components, a set of acceptable intervals around their nominal values must be defined. In this article, these intervals are called nominal ranges and have been chosen as  $\pm$  15%. Variations inside the specified ranges are considered acceptable as they guarantee an output ripple of less than 10% and CCM operation.

## B. Prototype of the Synchronous Zeta Converter

To verify the performance of the prognostic method, a physical Zeta converter prototype has been built, as shown in Fig. 2. Given the simple topology of the converter, a single printed circuit board (PCB) has been used, and several test points have been included to obtain the measurements of all voltages across the components, while current measurements are not needed by the proposed method.

Since the main purpose of the analysis is to detect the variation of the passive components, the positioning of the inductors has been chosen to facilitate their replacement and different capacitor values have been obtained by connecting several elements in parallel. The two switches are *N*-channel STC3022AL power MOSFETs. The other elements of the circuit are given in Table II.

As shown in Fig. 2, there are four different input/output (I/O) sections in the PCB: An external 24 V power supply is used to supply the integrated power MOSFET gate drivers.

Two BNC connectors are used to inject the control signals with opposite phases and, finally, the other two I/O sections are used to apply the dc source and power the load.

TABLE II CIRCUIT ELEMENTS

| Sign       | Fu                         | Full Name    |              | Туре                                |                              |  |

|------------|----------------------------|--------------|--------------|-------------------------------------|------------------------------|--|

| E1-E2      | MGJ61                      | D242005DC    | 5.7kVD       | 5.7kVDC Isolated 6W Gate Drive      |                              |  |

|            |                            |              | SI           | SIP DC-DC Converter                 |                              |  |

| E3         | 150                        | 3-2411WI     |              | Isolated 3W DC-DC Converter         |                              |  |

| E4-E5      | 1EDC60H12AHXUMA1           |              | Single Ch    | Single Channel Isolated IGBT driver |                              |  |

|            | TABLE III<br>Fault Classes |              |              |                                     |                              |  |

| N<br>class | $L_1(\mu H)$               | $L_2(\mu H)$ | $C_1(\mu F)$ | $C_2(\mu F)$                        | Working<br>Condition         |  |

| 0          | (323÷437)                  | (323÷437)    | (1.2÷1.6)    | (1.2÷1.6)                           | Nominal<br>Condition         |  |

| 1          | (38÷323)                   | (323÷437)    | (1.2÷1.6)    | (1.2÷1.6)                           | Problem<br>on L <sub>1</sub> |  |

| 2          | (323÷437)                  | (38÷323)     | (1.2÷1.6)    | (1.2÷1.6)                           | Problem<br>on L <sub>2</sub> |  |

| 3          | (323÷437)                  | (323÷437)    | (0.8÷1.2)    | (1.2÷1.6)                           | Problem<br>on C <sub>1</sub> |  |

| 4          | (323÷437)                  | (323÷437)    | (1.2÷1.6)    | (0.8÷1.2)                           | Problem<br>on C <sub>2</sub> |  |

## III. PROGNOSTIC PROCEDURE: THEORETICAL CONCEPTS

## A. Fault Classes

This article proposes a prognostic approach based on timedomain measurements of four voltages. The main objective is to identify the variation of the components outside the nominal range in the case of a single failure hypothesis. This means that only one component can change at a time and five classes of failure are considered.

Table III summarizes these classes, where the malfunction condition of the inductors shows a reduction in a proportion  $(15\div90)\%$  with respect to the nominal value and that of the capacitors in a proportion  $(15\div40)\%$ . These intervals were chosen to test the effectiveness of the prognostic method even during discontinuous conduction mode.

Many factors, such as aging or deterioration due to abnormal environmental conditions, can lead to the variation of the passive component values and this modifies the converter working conditions. The most common failure modes for inductors are short circuits between turns and the saturation of the magnetic core. Therefore, the malfunction conditions of  $L_1$  and  $L_2$  only result in a reduction of the inductance value below the nominal range. For capacitors  $C_1$  and  $C_2$ , the most common causes of failure are aging, overload, and overtemperature. All these situations can produce a deterioration of the dielectric with a consequent reduction of their capacitance.

Several techniques can be found in the literature to introduce a prognostic method in passive circuits [30], [31]. However, the main problems are the ability of these methods to work online and their capability of identification of the components in the worst state of health. Moreover, these frequency-domain-based methods can fail when applied to time-varying circuits as dc–dc converters are.

To achieve the goal of this work, a machine learning technique is used, which is an MLMVN. It falls in the category of supervised learning algorithms and, therefore, it is necessary to use a dataset containing several examples of correct classifications. The dataset matrix contains a high number of samples  $N_S$  for each fault class and the corresponding index in the last column (1). Each sample consists of eight measurements: average values and ripples of the four voltages.

The voltages used are those across the passive components, and to understand their effectiveness, it is necessary to perform the testability evaluation

$$\begin{bmatrix} V_{L1m}^{1} & V_{L1r}^{1} & V_{L2m}^{1} & V_{L2r}^{1} & V_{C1m}^{1} & V_{C1r}^{1} & V_{C2m}^{1} & V_{C2r}^{1} & 0 \\ V_{L1m}^{2} & V_{L1r}^{2} & V_{L2m}^{2} & V_{L2r}^{2} & V_{C1m}^{2} & V_{C1r}^{2} & V_{C2m}^{2} & 0 \\ & & \vdots & & \\ V_{L1m}^{5N_{S}} & V_{L1r}^{5N_{S}} & V_{L2m}^{5N_{S}} & V_{C1m}^{5N_{S}} & V_{C1r}^{5N_{S}} & V_{C2r}^{5N_{S}} & 4 \end{bmatrix} .$$

$$(1)$$

### B. Testability Assessment

As mentioned before, the main idea of prognostic analysis is to use the voltages across the passive components to identify the working condition of the Zeta converter. In this sense, the choice of test points plays a fundamental role because it makes the fault classes distinguishable. In fact, the variation of one component introduces a change in multiple measurements. This change must be different from that introduced by the variation of other components. If the choice of measurements allows the identification of all classes without ambiguities, the circuit under test is completely testable. The index used to evaluate this feature is called testability, and it corresponds to the solvability degree of the failure equations, which contain the values of the passive components as unknowns and are obtained in the test points considered [20].

Testability evaluation for passive circuits can be performed in the frequency or time domain. In the first case, the frequency responses of the circuit are extracted at the selected test points for different frequency values. Subsequently, setting the analytical form of these functions equals the relative measurements, it is possible to obtain a system of failure equations. The symbolic approach proposed in [20] uses the Laplace formulation of each frequency response

$$h_k(\mathbf{s}, \boldsymbol{p}) = \frac{N(\mathbf{s}, \boldsymbol{p})}{D(s, \boldsymbol{p})} = \frac{a_0(s, \boldsymbol{p}) + \dots + a_n(s, \boldsymbol{p})s^{\boldsymbol{n}}}{b_0(s, \boldsymbol{p}) + \dots + b_n(s, \boldsymbol{p})s^{\boldsymbol{n}}}$$

(2)

where k is the index of one of the  $n_h$  functions and p is the vector of the  $n_p$  potentially defective components used as unknows. In this case, testability is defined as the rank of the Jacobian matrix obtained by deriving the equations of the system with respect to the passive components

$$T = \operatorname{rank}\left( \begin{bmatrix} \frac{\partial h_1(s, \boldsymbol{p})}{\partial p_1} & \cdots & \frac{\partial h_1(s, \boldsymbol{p})}{\partial p_{n_p}} \\ \vdots & \cdots & \vdots \\ \frac{\partial h_{n_h}(s, \boldsymbol{p})}{\partial p_1} & \cdots & \frac{\partial h_{n_h}(s, \boldsymbol{p})}{\partial p_{n_p}} \end{bmatrix} \right).$$

(3)

The time-domain approach is less common, but it fits well to time-variant circuits as dc-dc converters are. In fact, in [21], I/O relationships or specific waveforms are sampled in steadystate conditions. Also, in this case, the analytical form of these quantities is used to obtain a set of failure equations in which the

unknowns are the components and the inputs are kept constant. Therefore, the symbolic vector of the sampled quantities is

$$\boldsymbol{y_T}(\boldsymbol{p}, \boldsymbol{u_o}) = [\boldsymbol{y}(\mathbf{t_1}, \boldsymbol{p}, \boldsymbol{u_o}), \dots, \boldsymbol{y}(\mathbf{t_{n_t}}, \boldsymbol{p}, \boldsymbol{u_o})]$$

(4)

where  $u_0$  contains the constant input samples and p is still the vector of the unknown parameters. Introducing the vector of the measurements  $y_T^*$ , it is possible to obtain the system of the fault diagnosis equations (5) whose Jacobian allows the calculation of testability

$$\boldsymbol{y}_{\boldsymbol{T}}(\boldsymbol{p},\boldsymbol{u}_0) = \boldsymbol{y}_{\boldsymbol{T}}^*.$$

(5)

In general, if the system of equations is completely solvable, then the testability is maximum and equal to the total number of passive components belonging to the circuit.

If, on the other hand, the testability is less than the total number of variable components, there are two or more elements that introduce the same variation on the measurements. This means that it is possible to detect the problem, but the specific component causing the improper converter operation cannot be located. In such a case, these elements belong to the same ambiguity group, which is defined as the set of components that cannot be simultaneously considered defective because they introduce indistinguishable variations on the selected measurements.

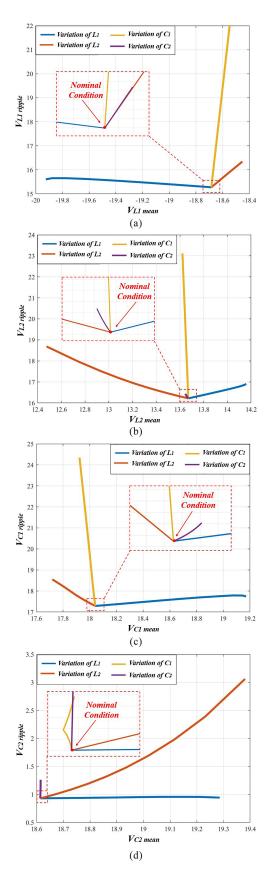

In the case of the time-variant circuit, the complexity of the method increases because the converter circuit goes through multiple topologies inside a switching period. This means that different testability ratings can be obtained in each situation, and the computational cost significantly increases, as reported in [21] and [32]. For this reason, in this article, a graphical evaluation of testability is proposed for the prognostic analysis of the Zeta converter. To achieve this goal, the Simulink model described above is managed by a MATLAB script, which sets the gradual variation of the components from the nominal value up to the malfunction conditions, as given in Table III. According to the single failure hypothesis, these variations are not simultaneous. For each situation, measurements of the four voltages are carried out and, consequently, the corresponding ripples and mean values are calculated. By plotting these measurements in a two-dimensional graph with the average values on the horizontal axis and the ripples on the vertical axis, the Zeta converter testability is studied. Fig. 3 shows the plots obtained by setting  $V_s = 15$  V. Here, the testability is maximum because there are no overlapping curves repeated in all the situations.

In general, the presence of two or more curves very close to each other indicates a possible reduction in testability because the variations of the components introduce the same effect on the measurement. If this situation is repeated for each graph, the corresponding components are indistinguishable, and it is necessary to add new measurements or modify some test points. In the case of the Zeta converter, there are no critical situations, and the testability is maximum.

Furthermore, the analysis of Fig. 3 allows the reduction of the measurements to only two voltages. In fact, the situation of partial ambiguity, as shown in Fig. 3(a), between the red and purple lines could be compensated by the distance of these curves, as shown in Fig. 3(b).

The same is for purple and yellow plots, as shown in Fig. 3(c)and (d). Therefore, the possibility of monitoring the Zeta

Fig. 3. Testability curves. (a) Voltage on  $L_1$ . (b) Voltage on  $L_2$ . (c) Voltage on  $C_1$ . (d) Voltage on  $C_2$ .

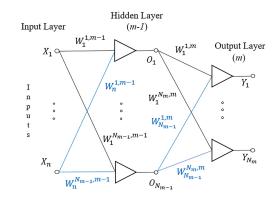

Fig. 4. General structure of the MLMVN-based classifier.

converter by using only two voltage measurements is one of the crucial aspects to verify through experimental tests. This not only avoids current measurements but also significantly reduces the number of test points.

# IV. MULTILAYER NEURAL NETWORK WITH MULTIVALUED NEURONS

The smart tool proposed in this article to classify the state of health of the Zeta converter is based on an MLMVN with three layers. It is a feedforward neural network trained through a backpropagation procedure [23]. One of the most important advantages over other neural networks is the absence of derivative terms in the learning rule [33]. This aspect, in addition to facilitating the correction of the weights, allows to speed up the learning process by introducing batch algorithms [24]. The main characteristic of this neural network is the complex nature of the weights and the outputs. Fig. 4 shows the global structure of the classifier used in this article, where  $W_i^{k,m}$  is the *i*th weight of the *k*th neuron belonging to the last layer (called layer *m*),  $n_{(m-1)}$  is the number of neurons belonging to the output layer, and  $(X_1, X_2, ..., X_n)$  are the inputs.

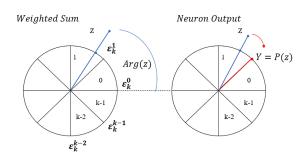

The elementary unit of the classifier is the MVN, which can be used in its continuous or discrete version. In the first case, the following activation function is used:

$$P(z) = e^{j\operatorname{Arg}(z)} = z/|z| \tag{6}$$

where  $\operatorname{Arg}(z)$  is the argument of the weighted sum of the inputs called *z*. This term is a complex number calculated as follows:

$$z = W_0 X_0 + \sum_{i=1}^n W_i X_i \tag{7}$$

where  $W_i$  describes the *i*th weight of the considered MVN and  $X_i$  represents the corresponding *i*th input.

Since the main objective of this work is to solve a classification problem, the output neurons present a discrete activation function, as shown as follows:

$$P(z) = \varepsilon_k^j = e^{i2\pi j/k}, \text{ if } 2\pi j/k \le \arg(z) \le 2\pi (j+1)/k.$$

(8)

This means that each neuron belonging to the output layer divides the complex plane into k equal sectors, and its output corresponds to the lower border of the sector that contains the

Fig. 5. Schematic representation of the functioning of discrete output neurons.

TABLE IV FAULT CLASSES AND OUTPUT VALUES

| Class | Description          | Output<br>Neuron<br>1 | Output<br>Neuron<br>2 | Output<br>Neuron<br>3 | Output<br>Neuron<br>4 |

|-------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0     | Nominal Condition    | 0                     | 0                     | 0                     | 0                     |

| 1     | Malfunction on $L_1$ | 1                     | 0                     | 0                     | 0                     |

| 2     | Malfunction on $C_1$ | 0                     | 1                     | 0                     | 0                     |

| 3     | Malfunction on $L_2$ | 0                     | 0                     | 1                     | 0                     |

| 4     | Malfunction on $C_2$ | 0                     | 0                     | 0                     | 1                     |

When the output of a binary neuron is 0, it means that the weighted sum *z* falls in the upper half plane and the complex value of this output is (1+j0).

When the output of a binary neuron is 1, it means that the weighted sum z falls in the lower half plane and the complex value of this output is (-1+j0).

weighted sum of the inputs. Fig. 5 summarizes the functioning of discrete neurons, highlighting the concept of weighted sum and the division into sectors of the complex plane.

In this article, the output neurons are binary, and this means that each of them creates two sectors: the first corresponds to the upper half plane  $[0, \pi)$  and is encoded by the value 0, and the second corresponds to the lower half plane  $[\pi, 2\pi)$  and is identified by the value 1. Consequently, the first sector of each neuron indicates the nominal condition of the corresponding analog component, while the second sector is used to describe the presence of a malfunction. This means that four neurons are used in the output layer, one for each electrical component, and the nominal condition of the converter corresponds to a combination of four zeros. It should be noted that the first output neuron is used to detect a malfunction on the inductor  $L_1$ , the second neuron is used to detect a problem on  $C_1$ , the third output indicates a change in  $L_2$ , and the last neuron is used to describe an abnormal working condition of the capacitor  $C_2$ .

Table IV summarizes the fault classes used in this article and the corresponding values of the outputs.

Therefore, the desired classes shown in the last column of the dataset matrix (1) must be converted in the corresponding output combinations during the training phase. In this way, it is possible to calculate the error for each output neuron and apply the backpropagation procedure. The error terms

$$\delta_{k,m}^{s} = \frac{D_{k,m}^{s} - Y_{k,m}^{s}}{n_{m-1} + 1} \tag{9}$$

are defined as the normalized differences between the complex number corresponding to the lower border of the desired sector  $D^{s}_{k,m}$  and that of the sector containing the current weighted

sum of the inputs  $Y_{k,m}$ . By using the standard backpropagation procedure, the correction rule shown in (10) is repeated for each sample of the dataset s ( $s = 1, ..., N_s$ )

$$\Delta W_i^{k,m} = \frac{\alpha_{k,m}}{(n_{m-1}+1) \left| z_{k,m}^s \right|} \delta_{k,m}^s \bar{Y}_{i,m-1}^s \tag{10}$$

where  $\Delta W_i^{k,m}$  is the correction for the *i*th weight of the *k*th neuron belonging to the layer *m*,  $\alpha_{k,m}$  is the corresponding learning rate,  $n_{m-1}$  is the number of the inputs equal to the number of outputs of the previous layer,  $|z^s_{k,m}|$  is the magnitude of the weighted sum,  $\delta^s_{k,m}$  is the output error, and  $\bar{Y}^s_{i,m-1}$  is the conjugate transposed of the input. It should be noted that (10) refers to the output layer but can be easily adapted for the correction of hidden neurons without introducing mathematical differences and by calculating the propagation of errors as follows:

$$\delta_{k,m-1}^{s} = \frac{1}{n+1} \sum_{i=1}^{n_m} \delta_{i,m}^{s} \left( W_k^{i,m} \right)^{-1}.$$

(11)

Therefore, the standard procedure used to train the MLMVNbased classifier can be summarized as follows: Each example belonging to the dataset is processed individually and the last element of the row is used to calculate the desired combination of the outputs, as given in Table IV. Since binary neurons are used in the last layer, all the desired outputs equals zero correspond to the lower border of the upper half plane (1+j0), while the desired output equals one corresponds to the lower border of the interval  $[\pi, 2\pi)$ , which is (-1+j0). Once the desired outputs are calculated, all complex weights are initialized to random values and the inputs are processed to obtain the current outputs. Starting from these values, the output errors are calculated (9) and the correction of each weight is defined individually (10) after having propagated the error from the last layer to the first (11).

It is also possible to reduce the computational cost of the learning procedure by applying a batch algorithm [24]. In this case, the output error calculated for each neuron and each sample is saved in a matrix at the end of every training epoch. Since the number of the samples belonging to the dataset is higher than the number of the inputs, some different techniques can be used, such as Q-R decomposition or singular value decomposition, for calculating the correction of the weights.

## V. EXPERIMENTAL PROCEDURE

The experimental procedure proposed here is organized as follows.

- 1) The first step is the testability evaluation of the Zeta converter using its Simulink model.

- Starting from the testability curves, it is possible to select the best test points avoiding ambiguity situations and to create the dataset matrix directly from the Simulink model.

- 3) The simulated voltage measurements belonging to the dataset refer to every possible working condition of the converter, and they are used to train the MLMVN-based classifier in the MATLAB environment.

- 4) Once the training phase has been completed, the performance of the classifier in recognizing the state of health of the Zeta converter is verified using real measurements extracted from the prototype.

- 5) To obtain real measurements of each possible working condition, passive components are substituted with others having different values.

Note that the creation of the dataset is completely carried out in Simulink by using the Zeta converter model without introducing real measurements in the training phase. Therefore, a MATLAB script is used to generate 100 samples ( $N_S = 100$ ) for each fault class. This means that for any class of Table III, 100 random values are generated for each component in both the nominal and the malfunction ranges. These values are used in Simulink to simulate the operation of the converter and extract the voltages across the passive components with a switching frequency of 50 kHz and a fixed D = 0.6. As a result, the dataset matrix is created, as shown in (1).

A  $5 \div 20$  V range is considered for the input voltage. In this way, it is possible to simulate the operation of the monitoring system in the presence of a variable power source. During the training phase, only four values are used: 5, 10, 15, and 20 V. Instead, different values than those utilized for the training, belonging to the range  $(5 \div 20)$  V, are used in the experimental validation. This verifies the generalization capability of the classifier and facilitates the training phase. Similarly, to obtain a robust classification system with respect to load variations, it is necessary to include resistance R values different from the nominal one during the training phase. In particular, to maintain a high classification rate (CR), all possible operating conditions must be considered in correspondence with all possible combinations of input voltage/load resistance. Therefore, variations in input source and load resistance pose no problem for classification performance when properly considered during the training phase. Obviously, the greater is the number of possible variations, the more time it takes to create the dataset matrix and train the neural classifier. The computational cost in extremely variable situations represents the main limitation of the proposed classifier, whose hidden layer must be modified according to the case studied.

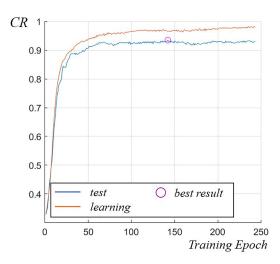

Once the dataset has been obtained, it is necessary to train the MLMVN and the authors developed a MATLAB application to achieve this purpose. The implemented backpropagation procedure is based on the Q-R decomposition, and this allows the reduction of training times and computational efforts. As described above, the last element of the rows belonging to the dataset matrix is converted to the desired outputs of the binary neurons in the last layer. The desired values of the outputs are complex numbers used to calculate the error of each sample. These errors are saved in a specific matrix and, once all samples have been processed, the Q-R decomposition is used to calculate the best corrections of the weights. It should be noted that the hold out validation method is implemented: 80% of the dataset is used to calculate the corrections (learning phase) and the remaining 20% is used to verify the classifier performance (test phase). The succession of the learning phase and the test phase represents a training epoch. The quality of the classification is evaluated in both phases through the CR, which is defined

Fig. 6. Results obtained during the training phase using an MLMVN with 60 neurons in the hidden layer and setting *"Mag-Phase"* mode.

as the ratio between the correctly classified samples and the total number of samples. The most significant CR is calculated during the test phase because it refers to data not used for the correction of the weights during the previous training epochs. The cross-validation method can be introduced to process all the information belonging to the dataset for both the training and test phases, obtaining a more accurate performance evaluation. The MATLAB application presented here offers both types of validation and the CR considered below is the one obtained in the test phase through the cross-validation method. The MLMVN developed by the authors can use the input measurements in three different ways. The first of them is the most used in the literature and generates a complex number starting from each real measurement. In the other two cases, each pair of dataset columns is used to create the corresponding complex numbers. The main characteristics of these methods are summarized as follows.

1) "Single Input" mode:

Each real measurement belonging to the dataset is used as the phase of a complex number with magnitude equals 1.

2) "Mag-Phase" mode:

In this case, the numbers belonging to the first column of each pair is the magnitude of the complex numbers, while the second column contains the phases.

3) "Real-Imag" mode:

The numbers belonging to the first column of each pair is the real parts of the complex numbers, while the second column is used to create the imaginary parts.

These three solutions are considered and compared during the simulations and the experimental tests.

The first result, as shown in Fig. 6, refers to the training procedure performed with 60 neurons in the hidden layer and setting the "Mag-Phase" mode of the MLMVN.

The CR obtained during the test phase (blue line) is higher than 94% and good performance is confirmed from a practical point of view using the experimental setup, as shown in Fig. 7. Two external generators are used to apply the dc source and the PCB 24 V supply voltage; a function generator with an auxiliary

Fig. 7. Experimental setup to obtain real measurements.

TABLE V CLASSIFICATION RESULTS

| MLMVN<br>setup | CR%<br>learning phase | CR%<br>test phase | CR% real measurements |

|----------------|-----------------------|-------------------|-----------------------|

| Mag-Phase      | 96.5                  | 94.75             | 89.47                 |

| Real-Imag      | 98.25                 | 97.75             | 78.95                 |

| Single Input   | 92                    | 87.5              | 73.68                 |

These results are obtained using ripples and mean values of the voltages extracted from four test points. The 60 neurons are used in the case of "Mag-Phase" mode and 90 neurons in the case of "Real-Imag" and "Single Input" modes.

circuit developed by the authors is used to create the phase opposite 5 V control signals. The voltages on the passive components are measured by an oscilloscope and imported to MATLAB to be processed by the neural classifier. It is necessary to point out that, to obtain the measurements in the fault conditions, the analog components are replaced with others having a different value or, as in the case of capacitors, one of the elements in parallel is eliminated.

The results obtained during the training phase and those obtained by processing real measurements are summarized in Table V. It should be noted that the hyperparameters of the classifier are chosen through a heuristic approach, starting from a given number of neurons, 20 in our case, and increasing up to 120.

Since the testability curves show the possibility of using only two measurements, two experimental tests have been carried out separately, considering the voltages on the inductors and those on the capacitors. The results obtained in these cases are given in Table VI.

The results obtained by using only two measurements confirm the testability assessment described above. As for the voltages on the inductors, the ambiguity, as shown in Fig. 3(a) and (b), does not allow to exceed a 50% CR with real measurements. Therefore, this solution cannot monitor the operation of the Zeta converter with an acceptable level of accuracy. On the other hand, by using the voltages across the capacitors, it is possible to reach a CR as high as 80%. In this case, the designer can decide whether to prefer the classification accuracy by measuring four

TABLE VI CLASSIFICATION RESULTS

| MLMVN<br>setup | Ripple<br>Voltages | CR%<br>learning<br>phase | CR%<br>test phase | CR%<br>real<br>measurements |

|----------------|--------------------|--------------------------|-------------------|-----------------------------|

| Mag-Phase      | $VL_1 VL_2$        | 68.13                    | 67.75             | 47.37                       |

| Mag-Phase      | $VC_1 VC_2$        | 82.25                    | 80.25             | 78.95                       |

These results are obtained using ripples and mean values of the voltages extracted from two test points. The 30 neurons are used in the hidden layer to process  $VL_1$  and  $VL_2$ . The 60 neurons are used for  $VC_1$  and  $VC_2$ .

### TABLE VII CLASSIFICATION RESULTS

| MLMVN     | CR%            | CR%        | CR% real measurements |

|-----------|----------------|------------|-----------------------|

| setup     | learning phase | test phase |                       |

| Mag-Phase | 96.88          | 95         | 94.74                 |

These results are obtained using only ripple measurements and four test points. The 70 neurons belong to the hidden layer of the MLMVN.

voltages or to reduce the intrusive level and accept a lower accuracy.

Furthermore, the results, as given in Table V, allow to conclude that the performances obtained in "Real-Imag" mode are slightly better than those obtained in "Mag-Phase" during the training procedure. On the other hand, by processing real measurements, the best result is obtained in "Mag-Phase" mode. This situation is caused by the small differences between the Zeta converter model and its prototype. In fact, the presence of parasitic effects makes the real behavior of the converter slightly different than that simulated, and this mostly affects the average value of the voltages. Since the "Mag-Phase" mode creates complex inputs without changing the information content of the ripple measurements, it results in better classifications with real measurements.

Starting from these considerations, new tests have been carried out using only ripples in the dataset matrix. These results are given in Table VII.

Therefore, the best classification result obtained on real measurements is carried out considering only ripples. In this case, four test points are still used, but the processing of the measurements is facilitated. To compare the best performance of the MLMVN with those of other machine learning techniques, several algorithms based on different theoretical approaches were applied to the same dataset. Results obtained with Bayesian classifiers and decision-tree-based classifiers are not presented because they do not exceed 80% CR during the training phase. The performances of a quadratic support vector machine (SVM) and a K-nearest neighbor (KNN) classifier are presented in Table VIII, because they are comparable with those of the MLMVN. In particular, the SVM algorithm is slightly better than the KNN classifier and very close to the MLMVN performance using both ripples and average voltage values. However, the best result obtained by applying MLMVN on ripple measurements is not achieved by any other technique.

Summing up, the neural classifier based on MLMVN results in an excellent performance by using four test points: CR is close to 95% during the training phase and 90% with real measurements. The monitoring method does not use current measurements,

|                            | MLMVN real measurements | SVM real measurements | KNN real<br>measurements<br>(K=1) |

|----------------------------|-------------------------|-----------------------|-----------------------------------|

| Mean Values<br>and Ripples | 89.47                   | 89.47                 | 84.21%                            |

| Only Ripples               | 94.74                   | 78.95                 | 75%                               |

TABLE VIII COMPARISON BETWEEN MLMVN AND SVM

These results are obtained using only ripple measurements and four test points. The 70 neurons belong to the hidden layer of the MLMVN.

which are more difficult to obtain, but only the voltages across all the passive components. Using only the voltages across the capacitors, the intrusive level of the prognostic system is lowered, and the accuracy of the classification is reduced by 10%.

# VI. CONCLUSION

In this article, the prognostic analysis based on MLMVN was proposed, which allowed the monitoring of dc-dc converters by locating the occurrence of malfunctions in specific components. This method was suitable to organize maintenance and plan the replacement of the component in the worst state of health, thus, reducing recovery times and damages inside the system, the converter is utilized in. The experimental results obtained on a Zeta converter confirmed that the proposed method was an excellent tool for the classification of malfunctions because it results in a high accuracy level and, also, requires a low computational effort and a very fast classifier training phase as well. In addition, the low intrusive level and the use of voltage measurements facilitate the application of the procedure in very complex circuits. In this sense, the proposed testability study results in a tool useful for practical applications, by providing a procedure that is easily extractable to other converter topologies. As a further development, the performance obtained with real measurements could be improved by modeling the parasitic components typical of any practical converter circuit and the fault prevention referred to semiconductor devices will be explored.

#### REFERENCES

- [1] H. Tarzamni, F. P. Esmaeelnia, M. Fotuhi-Firuzabad, F. Tahami, S. Tohidi, and P. Dehghanian, "Comprehensive analytics for reliability evaluation of conventional isolated multiswitch PWM dc-dc converters," *IEEE Trans. Power Electron.*, vol. 35, no. 5, pp. 5254–5266, May 2020, doi: 10.1109/TPEL.2019.2944924.

- [2] H. Givi, E. Farjah, and T. Ghanbari, "A comprehensive monitoring system for online fault diagnosis and aging detection of non-isolated dc-dc converters' components," *IEEE Trans. Power Electron.*, vol. 34, no. 7, pp. 6858–6875, Jul. 2019, doi: 10.1109/TPEL.2018.2875830.

- [3] Z. Jia, Z. Liu, C.-M. Vong, and X. Liu, "Real-time response-based fault analysis and prognostics techniques of nonisolated dc–dc converters," *IEEE Access*, vol. 7, pp. 67996–68009, 2019, doi: 10.1109/AC-CESS.2019.2901390.

- [4] Z. Gao, C. Cecati, and S. X. Ding, "A survey of fault diagnosis and fault-tolerant techniques—Part I: Fault diagnosis with model-based and signal-based approaches," *IEEE Trans. Ind. Electron.*, vol. 62, no. 6, pp. 3757–3767, Jun. 2015, doi: 10.1109/TIE.2015.2417501.

- [5] Z. Gao, C. Cecati, and S. X. Ding, "A survey of fault diagnosis and fault-tolerant techniques—Part II: Fault diagnosis with knowledge-based and hybrid/active approaches," *IEEE Trans. Ind. Electron.*, vol. 62, no. 6, pp. 3768–3774, Jun. 2015, doi: 10.1109/TIE.2015.2419013.

- [6] L. Wen, X. Li, L. Gao, and Y. Zhang, "A new convolutional neural networkbased data-driven fault diagnosis method," *IEEE Trans. Ind. Electron.*, vol. 65, no. 7, pp. 5990–5998, Jul. 2018, doi: 10.1109/TIE.2017.2774777.

- [7] Y. Lei, F. Jia, J. Lin, S. Xing, and S. X. Ding, "An intelligent fault diagnosis method using unsupervised feature learning towards mechanical big data," *IEEE Trans. Ind. Electron.*, vol. 63, no. 5, pp. 3137–3147, May 2016, doi: 10.1109/TIE.2016.2519325.

- [8] T. Dragičević, P. Wheeler, and F. Blaabjerg, "Artificial intelligence aided automated design for reliability of power electronic systems," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 7161–7171, Aug. 2019, doi: 10.1109/TPEL.2018.2883947.

- [9] Z. Li, Y. Gao, X. Zhang, B. Wang, and H. Ma, "A model-data-hybriddriven diagnosis method for open-switch faults in power converters," *IEEE Trans. Power Electron.*, vol. 36, no. 5, pp. 4965–4970, May 2021, doi: 10.1109/TPEL.2020.3026176.

- [10] S. Dusmez, M. Bhardwaj, L. Sun, and B. Akin, "In situ condition monitoring of high-voltage discrete power MOSFET in boost converter through software frequency response analysis," *IEEE Trans. Ind. Electron.*, vol. 63, no. 12, pp. 7693–7702, Dec. 2016, doi: 10.1109/TIE.2016.2595482.

- [11] S. Dusmez, S. H. Ali, M. Heydarzadeh, A. S. Kamath, H. Duran, and B. Akin, "Aging precursor identification and lifetime estimation for thermally aged discrete package silicon power switches," *IEEE Trans. Ind. Appl.*, vol. 53, no. 1, pp. 251–260, Jan./Feb. 2017, doi: 10.1109/TIA.2016.2603144.

- [12] M. S. Haque and S. Choi, "Sparse kernel ridge regression assisted particle filter based remaining useful life estimation of cascode GaN FET," *IEEE Trans. Ind. Electron.*, vol. 68, no. 8, pp. 7516–7525, Aug. 2021, doi: 10.1109/TIE.2020.3000126.

- [13] B. Wang, Z. Li, Z. Bai, P. T. Krein, and H. Ma, "A redundant unit to form T-type three-level inverters tolerant of IGBT open-circuit faults in multiple legs," *IEEE Trans. Power Electron.*, vol. 35, no. 1, pp. 924–939, Jan. 2020, doi: 10.1109/TPEL.2019.2912177.

- [14] H. Guzman, F. Barrero, and M. J. Duran, "IGBT-gating failure effect on a fault-tolerant predictive current-controlled five-phase induction motor drive," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 15–20, Jan. 2015, doi: 10.1109/TIE.2014.2331019.

- [15] M. Aminian and F. Aminian, "A modular fault-diagnostic system for analog electronic circuits using neural networks with wavelet transform as a preprocessor," *IEEE Trans. Instrum. Meas.*, vol. 56, no. 5, pp. 1546–1554, Oct. 2007, doi: 10.1109/TIM.2007.904549.

- [16] M. Tadeusiewicz and S. Hałgas, "A method for local parametric fault diagnosis of a broad class of analog integrated circuits," *IEEE Trans. Instrum. Meas.*, vol. 67, no. 2, pp. 328–337, Feb. 2018, doi: 10.1109/TIM.2017.2775438.

- [17] S. Kiranyaz, A. Gastli, L. Ben-Brahim, N. Al-Emadi, and M. Gabbouj, "Real-time fault detection and identification for MMC using 1-D convolutional neural networks," *IEEE Trans. Ind. Electron.*, vol. 66, no. 11, pp. 8760–8771, Nov. 2019, doi: 10.1109/TIE.2018.2833045.

- [18] S.-H. Kim, D.-Y. Yoo, S.-W. An, Y.-S. Park, J.-W. Lee, and K.-B. Lee, "Fault detection method using a convolution neural network for hybrid active neutral-point clamped inverters," *IEEE Access*, vol. 8, pp. 140632–140642, 2020, doi: 10.1109/ACCESS.2020.3011730.

- [19] A. Luchetta *et al.*, "MLMVNNN for parameter fault detection in PWM dc–dc converters and its applications for buck and boost dc–dc converters," *IEEE Trans. Instrum. Meas.*, vol. 68, no. 2, pp. 439–449, Feb. 2019, doi: 10.1109/TIM.2018.2847978.

- [20] G. Fontana, A. Luchetta, S. Manetti, and M. C. Piccirilli, "An unconditionally sound algorithm for testability analysis in linear time-invariant electrical networks," *Int. J. Circuit Theory Appl.*, vol. 44, no. 6, pp. 1308–1340, Jun. 2016, doi: 10.1002/cta.2164.

- [21] G. Fontana, A. Luchetta, S. Manetti, and M. C. Piccirilli, "A testability measure for dc-excited periodically switched networks with applications to dc–dc converters," *IEEE Trans. Instrum. Meas.*, vol. 65, no. 10, pp. 2321–2341, Oct. 2016, doi: 10.1109/TIM.2016.2581438.

- [22] G. Fontana, A. Luchetta, S. Manetti, and M. C. Piccirilli, "A fast algorithm for testability analysis of large linear time-invariant networks," *IEEE Trans. Circuits Syst. I, Regular Papers*, vol. 64, no. 6, pp. 1564–1575, Jun. 2017, doi: 10.1109/TCSI.2016.2645079.

- [23] I. Aizenberg, Complex-Valued Neural Networks With Multi-Valued Neurons. New York, NY, USA: Springer, 2011.

- [24] I. Aizenberg, A. Luchetta, and S. Manetti, "A modified learning algorithm for the multilayer neural network with multi-valued neurons based on the complex QR decomposition," *Soft Comput.*, vol. 16, pp. 563–575, Apr. 2012, doi: 10.1007/s00500-011-0755-7.

- [25] K. Woranetsuttikul, K. Pinsuntia, N. Jumpasri, T. Nilsakorn, and W. Khan-Ngern, "Comparison on performance between synchronous single-ended primary-inductor converter (SEPIC) and synchronous ZETA converter," in *Proc. Int. Elect. Eng. Congr.*, 2014, pp. 1–4, doi: 10.1109/iEECON.2014.6925855.

- [26] A. M. Khatab, M. I. Marei, and H. M. Elhelw, "An electric vehicle battery charger based on zeta converter fed from a PV array," in *Proc. IEEE Int. Conf. Environ. Elect. Eng. IEEE Ind. Commercial Power Syst. Europe*, 2018, pp. 1–5, doi: 10.1109/EEEIC.2018.8494541.

- [27] V. Bist and B. Singh, "Power factor correction in a brushless dc motor drive using an isolated-Luo converter," in *Proc. 6th IEEE Power India Int. Conf.*, 2014, pp. 1–6, doi: 10.1109/POWERI.2014.7117627.

- [28] J. A. Ziani, M. J. B. Ghorbal, and S. Moussa, "Comparative study of boost and zeta converters in dc microgrid applications," in *Proc. 6th IEEE Int. Energy Conf.*, 2020, pp. 222–225, doi: 10.1109/ENERGY-Con48941.2020.9236476.

- [29] F. L. Luo, "Luo-converters, voltage lift technique," in Proc. 29th Annu. IEEE Power Electron. Specialists Conf., 1998, vol. 2, pp. 1783–1789, doi: 10.1109/PESC.1998.703423.

- [30] S. Halgas and M. Tadeusiewicz, "Improvement of the search method for parametric fault diagnosis of analog integrated circuits," in *Proc.* 23rd Int. Conf. Mixed Des. Integr. Circuits Syst., 2016, pp. 359–362, doi: 10.1109/MIXDES.2016.7529765.

- [31] D. K. Papakostas and A. A. Hatzopoulos, "A unified procedure for fault detection of analog and mixed-mode circuits using magnitude and phase components of the power supply current spectrum," *IEEE Trans. Instrum. Meas.*, vol. 57, no. 11, pp. 2589–2595, Nov. 2008, doi: 10.1109/TIM.2008.924932.

- [32] I. Aizenberg, M. Bindi, F. Grasso, A. Luchetta, S. Manetti, and M. C. Piccirilli, "Testability analysis in neural network based fault diagnosis of dc-dc converter," in *Proc. IEEE 5th Int. Forum Res. Technol. Soc. Ind.*, 2019, pp. 265–268, doi: 10.1109/RTSI.2019.8895583.

- [33] I. Aizenberg, "MLMVN with soft margins learning," IEEE Trans. Neural Netw. Learn. Syst., vol. 25, no. 9, pp. 1632–1644, Sep. 2014, doi: 10.1109/TNNLS.2014.2301802.

Francesco Grasso (Member, IEEE) received the master's degree in electronic engineering and the Ph.D. degree in electronic devices and circuits from the University of Florence, Florence, Italy, in 2000 and 2003, respectively.

He is currently an Assistant Professor with the Department of Electronics and Telecommunications, University of Florence. His research interests are in the areas of circuit theory, neural networks, and fault diagnosis of electronic.

Antonio Luchetta (Member, IEEE) received the master's degree in electronic engineering from the University of Florence, Florence, Italy, in 1993.

From 1995 to 2005, he was an Assistant Professor with the Department of Environmental and Physics Engineering, University of Basilicata, Potenza, Italy, and then with the Department of Electronics and Telecommunications, University of Florence, where he is currently an Associate Professor with the Department of

Information Engineering. His current research interests include circuit theory neural networks, symbolic analysis, and simulation of analog circuits.

Stefano Manetti (Member, IEEE) received the *Laurea* degree in electronic engineering from the University of Florence, Florence, Italy, in 1977.

From 1977 to 1979, he was a Research Fellow with Engineering Faculty, University of Florence. From 1983 to 1987, he was a Researcher with Electronic Engineering Department, University of Florence, where he was an Associate Professor of Network Theory, from 1987 to 1994. In 1994, he joined the University of

Basilicata, Potenza, Italy, as a Full Professor of Electrical Sciences. Since 1996, he has been a Full Professor of Electrical Sciences with the University of Florence, where he was the Dean with Engineering Faculty, from 2009 to 2013. His current research interests include circuit theory, neural networks, fault diagnosis of electronic circuits, and symbolic analysis of analog circuits.

Maria Cristina Piccirilli (Member, IEEE) received the *Laurea* degree in electronic engineering from the University of Florence, Florence, Italy, in 1987.

From 1988 to 1990, she was a Research Fellow with the University of Pisa, Pisa, Italy. From 1990 to 1998, she was a Researcher with the Department of Electronic Engineering, University of Florence, where she has been an Associate Professor of Network Theory, since 1998, and is currently with the Department of Informa-

tion Engineering. Her current research interests include circuit theory, analog filters, fault diagnosis of electronic circuits, neural networks, and symbolic analysis of analog circuits.

Alberto Reatti (Member, IEEE) received the M.Sc. degree in electronics engineering from the University of Florence, Florence, Italy, in 1988, and the Ph.D. degree in electrical engineering from the University of Bologna, Bologna, Italy, in 1993.

In 1992, he was an Associate Researcher with the Department of Electrical Engineering, Wright State University, Dayton, OH, USA. He has been an Associate Professor with the Department of Information Engineering, University

of Florence, since 2000. His current research interests include highfrequency resonant and pulsewidth modulation dc–dc power converters, modeling and control of converters, renewable power sources, energy saving, wireless power transfer, H2 storage, and reliability of switching power converters.

Marco Bindi (Graduate Student Member, IEEE) received the M.S. degree in electrical and automation engineering in 2018 from the University of Florence, Florence, Italy, where he is currently working toward the Ph.D. degree in electrical systems.

From 2019 to 2020, he was a Researcher with the Department of Information Engineering, University of Florence. His research interests include applications of neural networks for fault diagnosis in electrical power system, symbolic

analysis, and simulation of analog circuits.

Fabio Corti (Member, IEEE) received the M.S. degree in electrical and automation engineering and the Ph.D. degree in industrial engineering from the University of Florence, Florence, Italy, in 2016 and 2019, respectively.

He was a Postdoctoral Research Fellow with Consiglio Nazionale delle Ricerche, in 2020. He is currently a Postdoctoral Research Fellow with the University of Perugia, Perugia, Italy. His research interest includes modeling and control of dc–dc PWM and resonant converters, wireless

power transfer, and electric vehicle powertrain.