## FLORE

### Repository istituzionale dell'Università degli Studi di Firenze

# Closed-loop input impedance of PWM buck-derived DC-DC convertersProceedings of IEEE International Symposium on Circuits

Questa è la Versione finale referata (Post print/Accepted manuscript) della seguente pubblicazione:

Original Citation:

Closed-loop input impedance of PWM buck-derived DC-DC convertersProceedings of IEEE International Symposium on Circuits and Systems - ISCAS '94 / M.K. Zamierczuk;R.C. Cravens;A. Reatti. - ELETTRONICO. - 6:(1994), pp. 61-64. (Intervento presentato al convegno Circuits and Systems, 1994. ISCAS '94., 1994 IEEE International Symposium on) [10.1109/ISCAS.1994.409526].

Availability:

This version is available at: 2158/645176 since:

Published version: DOI: 10.1109/ISCAS.1994.409526

*Terms of use:* Open Access

La pubblicazione è resa disponibile sotto le norme e i termini della licenza di deposito, secondo quanto stabilito dalla Policy per l'accesso aperto dell'Università degli Studi di Firenze (https://www.sba.unifi.it/upload/policy-oa-2016-1.pdf)

Publisher copyright claim:

(Article begins on next page)

### Closed–Loop Input Impedance of PWM Buck–Derived DC–DC Converters

Marian K. Kazimierczuk, Robert C. Cravens, II Wright State University Department of Electrical Engineering Dayton, OH 45435, U. S. A.

Abstract— The small-signal closed-loop input impedance is derived for the PWM buck dc-dc converter operated in continuous conduction mode (CCM), taking into account all parasitic resistances. The plots of the closed-loop input impedance are shown versus frquency for four values of the equivalent series resistance of the capacitor.<sup>1</sup>

#### I. INTRODUCTION

A small-signal linear circuit model of the PWM buck converter has been developed, taking into account all parasitic resistances [1]-[3]. This derivation used an evergy conservation method. The current ripple in the inductor is neglected in [1], [2] and is taken into account in [3]. Openloop small-signal characteristics were illustrated using this model. The purpose of this paper is to present the derivation of the closed-loop input impedance of the voltagemode-controlled PWM buck dc-dc power converter with a proportional controller for CCM.

#### II. SMALL-SIGNAL CIRCUIT MODEL OF THE PWM BUCK CONVERTER

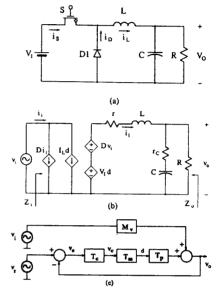

A circuit of the PWM buck converter is shown in Fig. 1(a). It consists of a power MOSFET as a switch S, a diode D1, an inductor L, and a filter capacitor C. The converter is fed by a dc input voltage source  $V_I$  and is loaded by a dc load resistance R. The switch is turned on and off at the switching frequency  $f_s = 1/T$  and the on-duty ratio is  $D = t_{on}/T$ , where  $t_{on}$  is the time interval during which the switch is on. Parasitic components associated with each circuit component, where  $r_{DS}$  is the MOSFET's onresistance,  $R_F$  is the diode forward resistance,  $V_F$  is the diode threshold voltage,  $r_L$  is the equivalent series resistance of inductor L, and  $r_C$  is the ESR of the filter capacitor C.

Fig. 1(b) depicts a small-signal model of this converter [1], where d is the ac component of the switch duty ratio,  $v_i$  is the ac component of the input voltage,  $v_o$  is the ac component of the output voltage,  $I_L$  is the dc component of the inductor current, and  $i_l$  is the ac component of the inductor current. Resistance r is an equivalent averaged resistance (EAR) and is given by [1]

$$r = Dr_{DS} + (1 - D)R_F + r_L.$$

(1)

Fig. 1(c) shows a block diagram of a closed-loop buck converter.  $T_p$  represents a small-signal model of the buck

Alberto Reatti Universty of Florence Department of Electronic Engineering 50139 Florence, Italy

Fig. 1: PWM buck converter. (a) Circuit. (b) Small-signal model (c) Block diagram of the closed-loop voltage-mode-controlled converter.

converter,  $T_m$  represents a PWM modulator,  $T_c$  represents a controller,  $M_v$  represents an input-to-output voltage transfer function,  $T_{ol}$  is the the open-loop control-to-output transfer function,  $v_c$  is the output voltage of the controller,  $v_e$  is the error signal applied to the input of the controller, and  $v_r$  is the ac component of the reference voltage. This is a two-input and a single-output system. It is driven by two independent sources,  $v_r$  and  $v_i$ . The ac component of the output voltage is

$$v_o(s) = \frac{T_{ol}}{1 + T_{ol}} v_r(s) + \frac{M_v(s)}{1 + T_{ol}} v_i(s).$$

(2)

The PWM buck-derived converters such as the forward, push-pull, half-bridge, and full-bridge converters (which contain transformers) have the same small-signal model and characteristics as the PWM buck converter [2]. Therefore, the transformer turns ratio n is included in the subsequent equations. The equivalent averaged resistance r is the only difference between these converters [2].

#### **III. OPEN-LOOP TRANSFER FUNCTIONS**

The small-signal model of Fig. 1(b) can be used to describe the converter performance for frequencies f up to

<sup>&#</sup>x27;This work was supported by the National Science Foundation under Grant ECS-8922695.

about one-half the switching frequency  $f_s$ . Using this model, one can derive the control-to-output (or duty ratio-to-output) transfer function in the s-domain

$v_o(s)$

$$T_{p}(s) \equiv \frac{1}{d(s)} |_{v_{i}(s)=0}$$

$$= \frac{V_{I}Rr_{C}}{nL(R+r_{C})} \frac{s + \frac{1}{Cr_{C}}}{s^{2} + s\frac{C(Rr_{C}+Rr+r_{C}r)+L}{LC(R+r_{C})}} + \frac{R+r}{LC(R+r_{C})}$$

$$= \frac{V_{I}R\omega_{r}^{2}}{n\omega_{z}(R+r)} \frac{s + \omega_{z}}{s^{2} + 2\xi_{r}\omega_{r}s + \omega_{r}^{2}}$$

(3)

where the frequency of the zero is

\_ / \

$$\omega_z = \frac{1}{Cr_C} \tag{4}$$

the corner frequency is

$$\omega_r = \sqrt{\frac{R+r}{LC(R+r_C)}} \tag{5}$$

and the damping ratio is

$$\xi_r = \frac{C(Rr_C + Rr + r_C r) + L}{2\sqrt{LC(R + r_C)(R + r)}}.$$

(6)

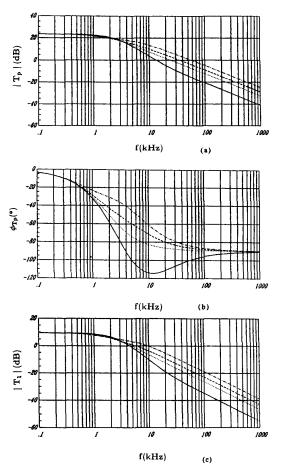

Fig. 2(a) and (b) shows plots of the magnitude and the phase of  $T_p$ . The characteristics of  $T_p$  are plotted for four values of  $r_C$  because they strongly depend on  $r_C$ .

The voltage transfer function of the PWM modulator is

$$T_m \equiv \frac{d(s)}{v_c(s)} = \frac{1}{V_{Tm}} \tag{7}$$

where  $V_{Tm}$  is the peak value of the ramp voltage of the PWM modulator. It is assumed that  $V_{Tm} = 5$  V, resulting in  $T_m = 0.2 = -14$  dB.

The control-to-output transfer function of the converter and the modulator is given by

$$T_1(s) \equiv \frac{v_o(s)}{v_c(s)} = T_m T_p(s)$$

$$= \frac{V_I R \omega_r^2}{n \omega_z V_{T_m}(R+r)} \frac{s + \omega_z}{s^2 + 2\xi_r \omega_r s + \omega_r^2}.$$

(8)

Fig. 2(c) depicts a Bode plot of  $|T_1|$ . The phase shift  $\phi_{T_1}$  of  $T_1$  is the same as the phase shift  $\phi_{T_p}$  and is depicted in Fig. 2(b).

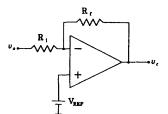

To obtain a wide bandwidth of the open-loop transfer function, a proportional controller is used. The controller which employs an inverting op-amp is shown in Fig. 3. Since the operation at high frequencies is of interest, the frequency response of the op-amp should be taken into account. For this reason, a pure proportional controller is difficult to realize. The voltage transfer function of the controller for the ac component is

$$T_c(s) \equiv \frac{v_c(s)}{v_e(s)} = \frac{A_{vo}}{1 + \frac{s}{\omega_{HJ}}} = \frac{A_{vo}}{1 + \frac{sA_{vo}}{\omega_1}}$$

(9)

Fig. 2: Control-to-output transfer function  $T_p = |T_p| e^{j\phi_{T_p}}$  and  $|T_1|$  for  $V_I = 30$  V, n = 1,  $L = 5 \mu$ H, C = 1 mF,  $R = 0.25 \Omega$ ,  $r = 0.15 \Omega$ , D = 0.3, and various values of  $r_C = 0.01$  (solid line), 0.03, 0.05, and 0.1  $\Omega$ . (a)  $|T_p|$  against f. (b)  $\phi_{T_p} = \phi_{T_1}$  against f. (c)  $|T_1|$  against f.

Fig. 3: Circuit diagram of the proportional controller.

where the low frequency gain is

$$A_{vo} = \frac{R_f}{R_i}.$$

(10)

The open-loop control-to-output transfer function is

$$T_{ol}(s) = T_c(s)T_1(s) = T_c(s)T_mT_p(s).$$

(11)

Plots of  $T_{ol}$  are shown in Fig. 4. The crossover frequency  $f_c$  of the open-loop transfer function |  $T_{ol}$  | is 27 to 100 kHz

Fig. 4: Open-loop transfer function  $T_{ol} = |T_{ol}| e^{j \phi_{T_{ol}}}$  for  $L = 5 \ \mu\text{H}, C = 1 \ \text{mF}, R = 0.25 \ \Omega, r = 0.15 \ \Omega, D = 0.3, A_{vo} = 14$ , and various values of  $r_C = 0.01$  (solid line), 0.03, 0.05, and 0.1  $\Omega$ . (a)  $|T_{ol}|$  against f. (b)  $\phi_{T_{ol}}$  against f.

for  $r_C$  ranging from 0.01 to 0.1  $\Omega$ . The phase margin is greater than 45°. Since the phase  $\phi_{T_{ol}}$  never crosses -180°, the gain margin cannot be determined.

The input-to-output (or line-to-output) voltage transfer function (which describes the input-output noise transmission), is

$$M_{v}(s) \equiv \frac{v_{o}(s)}{v_{i}(s)} |_{d(s)=0}$$

$$= \frac{DRr_{C}}{nL(R+r_{C})} \frac{s + \frac{1}{Cr_{C}}}{s^{2} + s\frac{C(Rr_{C}+Rr+r_{C}r)+L}{LC(R+r_{C})}} + \frac{R+r}{LC(R+r_{C})}$$

$$= \frac{DR\omega_{r}^{2}}{n\omega_{z}(R+r)} \frac{s + \omega_{z}}{s^{2} + 2\xi_{r}\omega_{r}s + \omega_{r}^{2}}.$$

(12)

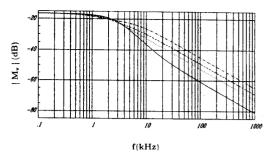

It follows from (12) that  $|M_v|$  increases with increasing D. Therefore,  $M_v$  should be considered for the maximum value of D. Plots of  $|M_v|$  are shown in Fig. 5.

The open-loop input impedance is

$$Z_i(s) \equiv \frac{v_i(s)}{i_i(s)} \mid_{d(s)=0}$$

$$= \frac{n^2 L}{D^2} \frac{s^2 + s \frac{C(Rr_C + Rr + r_C r) + L}{LC(R + r_C)} + \frac{R + r}{LC(R + r_C)}}{s + \frac{1}{C(R + r_C)}}$$

$$= \frac{n^2 L}{D^2} \frac{s^2 + 2\xi_r \omega_r s + \omega_r^2}{s + \omega_{cr}}$$

where

$$\omega_{cr} = \frac{1}{C(R+r_C)}.$$

(14)

Fig. 5: Magnitude of the open-loop input-to-output transfer function |  $M_v$  | against f for  $V_I = 30$  V, n = 1,  $L = 5 \mu$ H, C = 1 mF,  $R = 0.25 \Omega$ ,  $r = 0.15 \Omega$ , D = 0.3, and various values of  $r_C = 0.01$  (solid line), 0.03, 0.05, and 0.1  $\Omega$ .

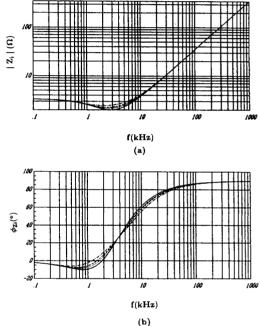

Fig. 6: Open-loop input impedance  $Z_i = |Z_i| e^{j\phi_{Z_i}}$  for D = 0.3, n = 1,  $L = 5 \mu$ H, C = 1 mF,  $R = 0.25 \Omega$ ,  $r = 0.15 \Omega$ , D = 0.3, and various values of  $r_C = 0.01$  (solid line), 0.03, 0.05, and 0.1  $\Omega$ . (a)  $|Z_i|$  against f. (b)  $\phi_{Z_i}$  against f.

For s = 0,

$$Z_i(0) = \frac{n^2(R+r)}{D^2}.$$

(15)

Fig. 6 shows plots of  $Z_i$  as a function of frequency.

#### IV. CLOSED-LOOP INPUT IMPEDANCE

The closed-loop input impedance can be derived as follows. Referring to the block diagram shown in Fig. 1(c) (13) and assuming  $v_r = 0$ ,

$$v_o = T_p d + M_v v_i \tag{16}$$

$$d = -v_o T_c T_m = -(T_p d + M_v v_i) T_c T_m.$$

(17)

64

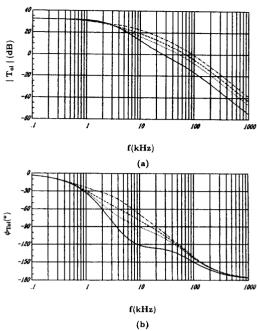

Fig. 7: Closed-loop input impedance  $Z_{icl} = |Z_{icl}| e^{j\phi_{Zicl}}$ for  $A_{vo} = 14$ ,  $f_1 = 1$  MHz,  $V_{Tm} = 5$  V, D = 0.3, n = 1,  $L = 5 \mu$ H, C = 1 mF,  $R = 0.25 \Omega$ ,  $r = 0.15 \Omega$ , D = 0.3, and various values of  $r_C = 0.01$  (solid line), 0.03, 0.05, and 0.1  $\Omega$ . (a)  $|Z_{icl}|$  against f. (b)  $\phi_{Zicl}$  against f.

Dividing (12) by (3) gives

$$M_v = \frac{D}{V_I} T_p. \tag{18}$$

Substitution of (11) and (18) into (17) yields

$$d = -\frac{T_c T_m M_v}{1 + T_c T_m T_p} v_i = -v_i \left(\frac{M_v}{T_p}\right) \left(\frac{T_{ol}}{1 + T_{ol}}\right)$$

$$= -\frac{DT_{ol}}{V_l (1 + T_{ol})} v_i. \tag{19}$$

Neglecting  $V_F$  in a dc model of the buck converter [1],

$$I_L = \frac{DV_I}{n(R+r)}.$$

(20)

Finally, the closed-loop input admittance is given by

$$Y_{icl} = \frac{1}{Z_{icl}} \equiv \frac{i_i}{v_i} = \frac{Di_l + I_L d}{nv_i}$$

$$= \frac{1}{Z_i} \frac{1}{1 + T_{ol}} - \frac{DI_L}{V_I} \frac{T_{ol}}{1 + T_{ol}}$$

$$= \frac{1}{Z_i} \frac{1}{1 + T_{ol}} - \frac{D^2}{n^2 (R + r)} \frac{T_{ol}}{1 + T_{ol}}$$

(21)

where  $i_l = n(Dv_i + V_I d)/(D^2 Z_i)$ . If s = 0 and  $|T_{ol}| > 1$  then

$$Z_{icl}(0) \approx -\frac{n^2(R+r)}{D^2} = -Z_i(0).$$

(22)

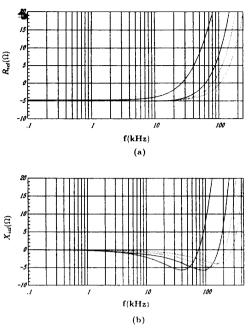

Fig. 8: Closed-loop input impedance  $Z_{icl} = R_{icl} + jX_{icl}$ for  $A_{vo} = 14$ ,  $f_1 = 1$  MHz,  $V_{Tm} = 5$  V, D = 0.3, n = 1,  $L = 5 \mu$ H, C = 1 mF,  $R = 0.25 \Omega$ ,  $r = 0.15 \Omega$ , D = 0.3, and various values of  $r_C = 0.01$  (solid line), 0.03, 0.05, and 0.1  $\Omega$ . (a)  $R_{icl}$  against f. (b)  $X_{icl}$  against f.

For  $f >> f_c$  and  $|T_{ol}| << 1$ ,  $Z_{icl} \approx Z_i(1+T_{ol}) \approx Z_i$ . Figs. 7 and 8 show plots of the closed-loop input impedance. It can be seen from Fig. 8(a) that the closed-loop input resistance  $R_{icl}$  is negative at low frequencies.

#### **V. CONCLUSIONS**

The small-signal closed-loop input impedance of the PWM buck-derived dc-dc power converters has been derived and illustrated for four values of the ESR of the filter capacitor. A proportional controller was used. Plots of the closedloop input-impedance have been shown. The closed-loop input resistance is negative at low frequencies. The results agree with those obtained from the state-space averaging method [4].

#### References

- D. Czarkowski and M. K. Kazimierczuk, "Circuit models of PWM dc-dc converters," Proceedings of the IEEE Nat. Aerospace and Electronic Systems Conference (NAECON'92), Dayton, OH, May 18-22, 1992, pp. 407-413.

- [2] D. Czarkowski and M. K. Kazimierczuk, "Static- and dynamiccircuit models of PWM buck-derived dc-dc converters," *IEE Proceedings, Pt. G, Circuits, Devices and Systems*, vol. 139, pp. 669-679, Dec. 1992.

- [3] D. Czarkowski and M. K. Kazimierczuk, "Energy-conservation approach to modeling PWM DC-DC converters," *IEEE Trans*actions on Aerospace and Electronic Systems, vol. 29, pp. 1059– 1063, July 1993.

- [4] R. D. Middlebrook and S. Ćuk, Advances in Switched-Mode Power Conversion, vols. I and II. Pasadena, CA, TESLACO, 1981.