### UNIVERSITÀ DEGLI STUDI DI FIRENZE DIPARTIMENTO DI INGEGNERIA DELL'INFORMAZIONE

# AN ONTOLOGICAL APPROACH SUPPORTING THE DEVELOPMENT OF SAFETY-CRITICAL SOFTWARE

DISSERTATION SUBMITTED IN PARTIAL FULFILLMENT

OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

IN INFORMATICS ENGINEERING, MULTIMEDIA AND TELECOMMUNICATIONS

#### Irene Bicchierai

Ph.D. Coordinator Prof. Luigi Chisci Advisors

Prof. Enrico Vicario

Prof. Giacomo Bucci

XXVI CICLO - 2011-2013

"...

fatti non foste a viver come bruti, ma per seguir virtute e canoscenza."

Dante, Inferno, Canto XXVI, vv. 119-120

# Acknowledgements

Innanzitutto vorrei ringraziare i miei Professori Enrico Vicario e Giacomo Bucci, per l'aiuto che mi hanno dato durante il lavoro di tesi, per avermi guidato dandomi spunti e suggerimenti durante questi tre anni, e soprattutto per la fiducia che hanno riposto in me.

Un grazie enorme a Laura. Per tutte le volte che ti ho chiesto aiuto e tu sei stata disponibile a darmelo, per tutte le volte che ci siamo ascoltate e capite. In questi anni mi hai insegnato tanto e spero di essere riuscita a mettere in pratica anche solo un po' dei tuoi insegnamenti.

Grazie a tutti i ragazzi che fanno parte, o hanno fatto parte, dell'STLab!!! Grazie a Lorenzo, Alessandro, Jacopo, Valeriano, Tommaso, Marco P., Marco M., Andrea, Fulvio, Simone. In particolare grazie a Carlo, con cui ho condiviso buona parte del lavoro di questa tesi. Grazie per le chiacchierate durante i pranzi in mensa, per i momenti piacevoli passati insieme, per i pranzi nel soppalco ...

E poi grazie alla mia famiglia, alle mie amiche, a Alessandra, alla mia cugina Giulia, per avermi sempre appoggiato e incoraggiato ad ottenere risultati sempre migliori.

Un grazie speciale ai miei genitori, Misia e Egidio, per come mi siete stati vicino in questi anni, per non avermi mai fatto mancare niente. Grazie per avermi assecondato in tutto ciò che mi piaceva e per aver accettato ogni mia scelta anche se talvolta non incontrava le vostre aspettative. Grazie perché se dovessi valere qualcosa come persona, il merito sarebbe soprattutto vostro.

E infine grazie a Leonardo, che, da fidanzato, in questi tre anni è diventato mio marito. Grazie per avermi sempre incoraggiato, sopportato e supportato, grazie per tutto l'amore che mi dai ogni giorno.

#### Abstract

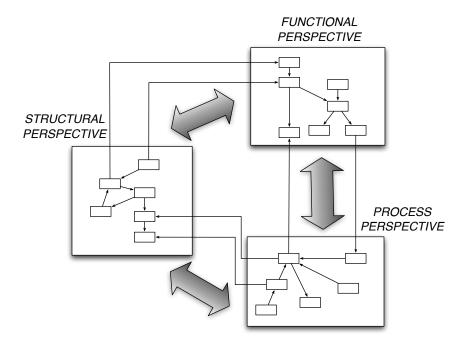

In several application domains, the development of safety-critical software is subject to certification standards which prescribe to perform activities depending on information relative to different stages of development. Data needed in these activities reflects concepts that pertain to three different perspectives: i) structural elements of design and implementation; ii) functional requirements and quality attributes; iii) organization of the overall process. The integration of these concepts may considerably improve the trade-off between reward and effort spent in verification and quality-driven activities.

This dissertation proposes a systematic approach for the efficient management of concepts and data involved in the development process of safety critical systems, illustrating how the activities performed during the life cycle can be integrated in a common framework. This thesis addresses the exploitation of ontological modeling and semantic technologies so as to support cohesion across different stages of the development life cycle, attaching a machine-readable semantics to concepts belonging to structural, functional and process perspectives. The formalized conceptualization enables the implementation of a tool leveraging well established technologies aiding the accomplishment of crucial and effort-expensive activities.

# Contents

| List of Acronyms |                                                                 |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

|------------------|-----------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| In               | Introduction                                                    |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

| 1                | Defining an ontology to systematize life cycle activities       |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

|                  | 1.1                                                             | Ontologies                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

|                  |                                                                 | 1.1.1                                             | RDF ed RDF Schema                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2  |  |  |  |  |

|                  |                                                                 | 1.1.2                                             | Ontology Web Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3  |  |  |  |  |

|                  |                                                                 | 1.1.3                                             | SPARQL Protocol and RDF Query Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6  |  |  |  |  |

|                  |                                                                 | 1.1.4                                             | Semantic Web Rule Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8  |  |  |  |  |

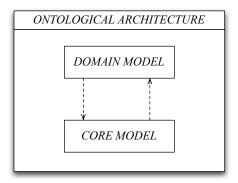

|                  |                                                                 | 1.1.5                                             | Ontological architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8  |  |  |  |  |

|                  | 1.2                                                             | Ontolo                                            | ogical formalization of three perspectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10 |  |  |  |  |

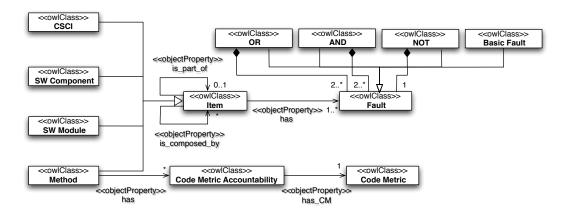

|                  |                                                                 | 1.2.1                                             | The second secon | 10 |  |  |  |  |

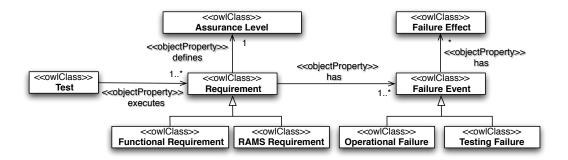

|                  |                                                                 | 1.2.2                                             | Functional perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11 |  |  |  |  |

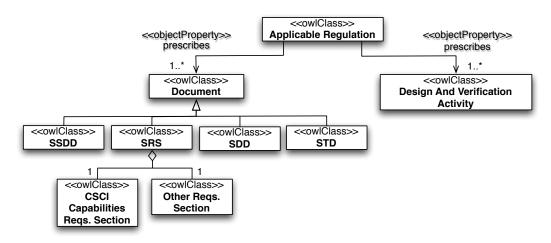

|                  |                                                                 | 1.2.3                                             | Process perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12 |  |  |  |  |

|                  | 1.3                                                             | Suppo                                             | rting dependability techniques through ontologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14 |  |  |  |  |

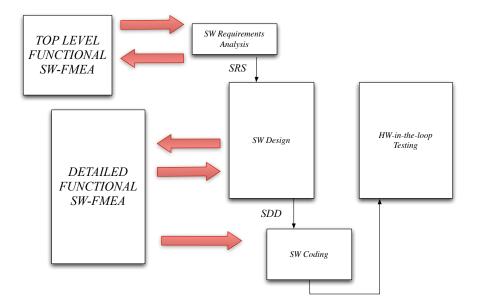

|                  |                                                                 | 1.3.1                                             | SW-FMEA and SW-FTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15 |  |  |  |  |

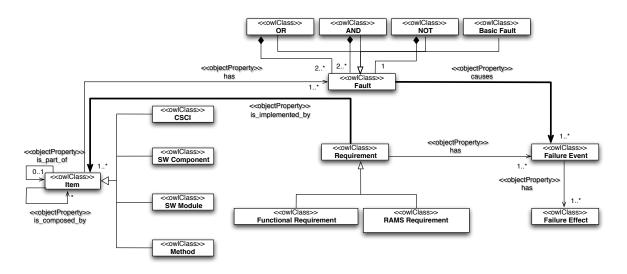

|                  |                                                                 | 1.3.2                                             | Ontological formalization of SW-FMEA and SW-FTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18 |  |  |  |  |

| 2                | Instantiating the ontology to systematize life cycle activities |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

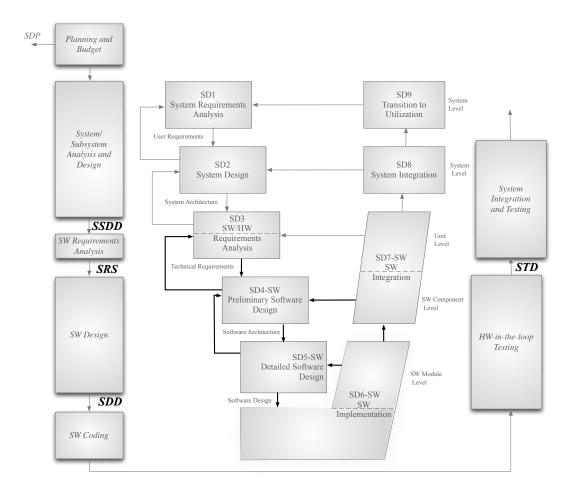

| 2                | 2.1                                                             | An industrial tailoring of the V-Model life cycle |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

|                  | 2.2                                                             | Conne                                             | cting different perspectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25 |  |  |  |  |

|                  |                                                                 | 2.2.1                                             | Tracing requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25 |  |  |  |  |

|                  |                                                                 | 2.2.2                                             | Following the documentation process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 |  |  |  |  |

|                  |                                                                 | 2.2.3                                             | Verifying activities of the development process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 |  |  |  |  |

| 3  | Casting UML-MARTE and pTPNs in the ontology |                                                   |                                                        |    |  |  |  |

|----|---------------------------------------------|---------------------------------------------------|--------------------------------------------------------|----|--|--|--|

|    | 3.1                                         | Forma                                             | I methods in an industrial SW process                  | 31 |  |  |  |

|    | 3.2                                         | rting the documentation process through UML-MARTE | 35                                                     |    |  |  |  |

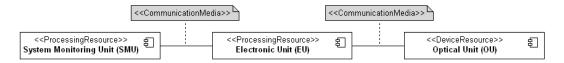

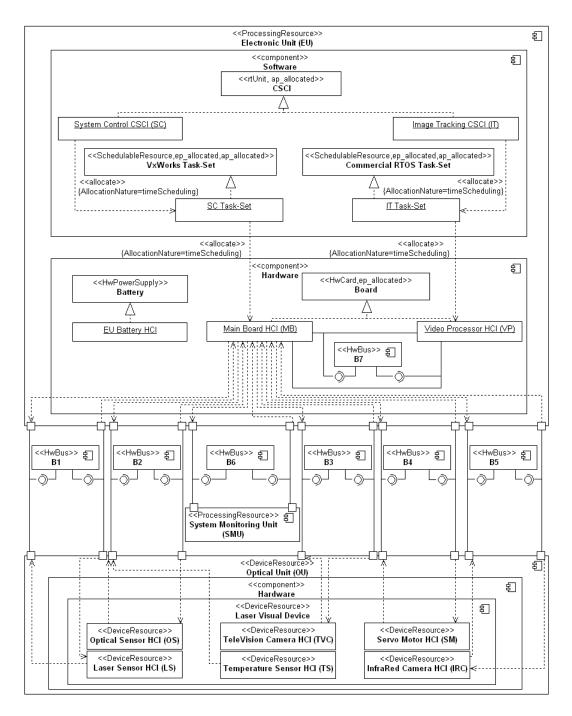

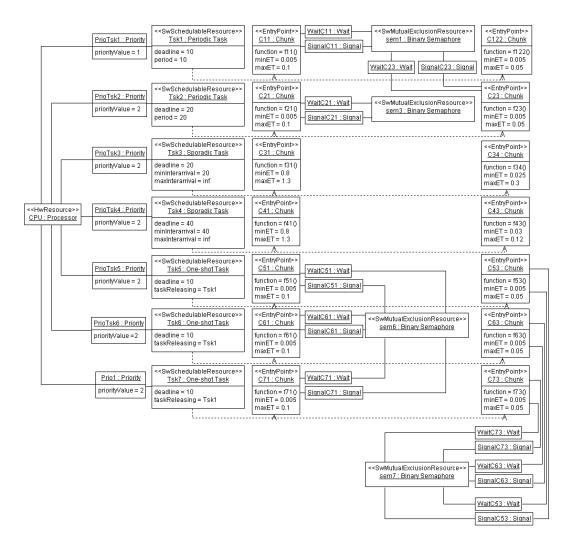

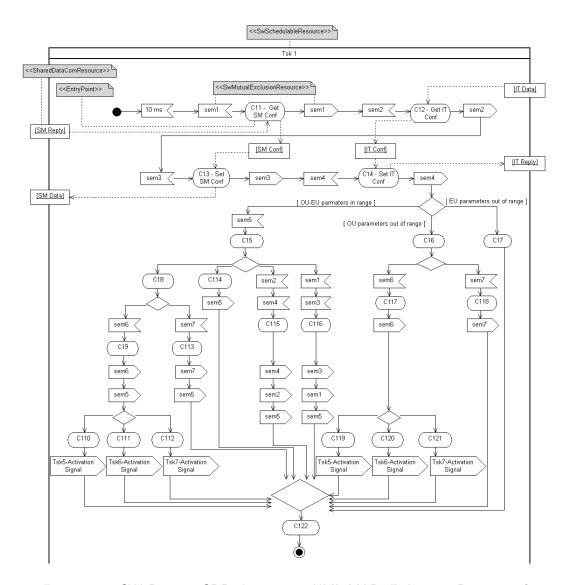

|    |                                             | 3.2.1                                             | System/Subsystem Analysis and Design and SSDD document | 35 |  |  |  |

|    |                                             | 3.2.2                                             | SW Requirements Analysis and SRS document              | 40 |  |  |  |

|    |                                             | 3.2.3                                             | SW Design and SDD document                             | 40 |  |  |  |

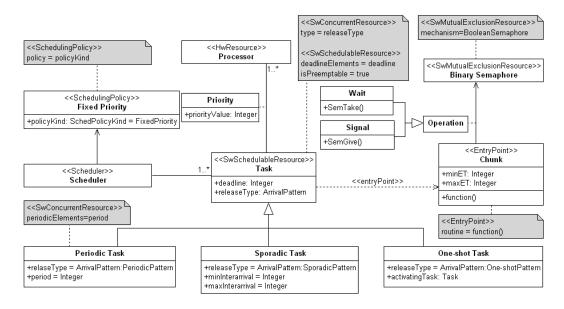

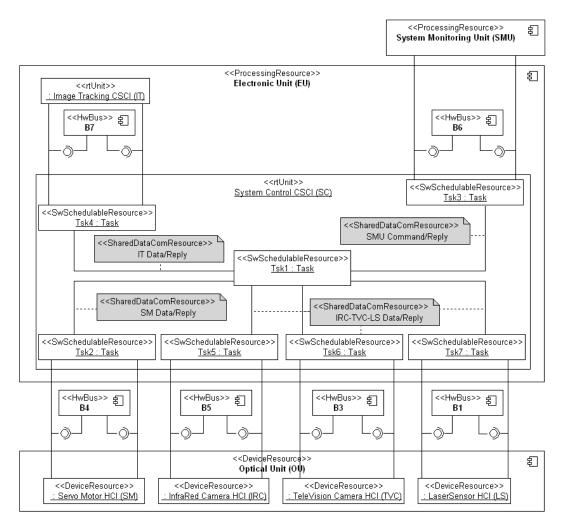

|    |                                             |                                                   | 3.2.3.1 Semi-formal specification through UML-MARTE    | 43 |  |  |  |

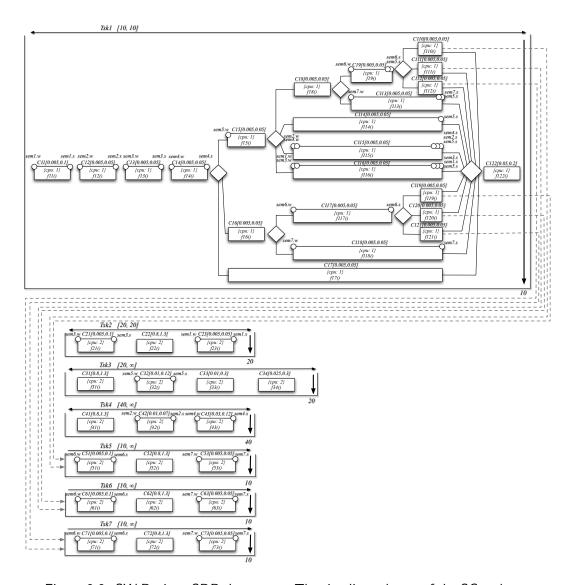

|    |                                             |                                                   | 3.2.3.2 Semi-formal specification through timelines    | 48 |  |  |  |

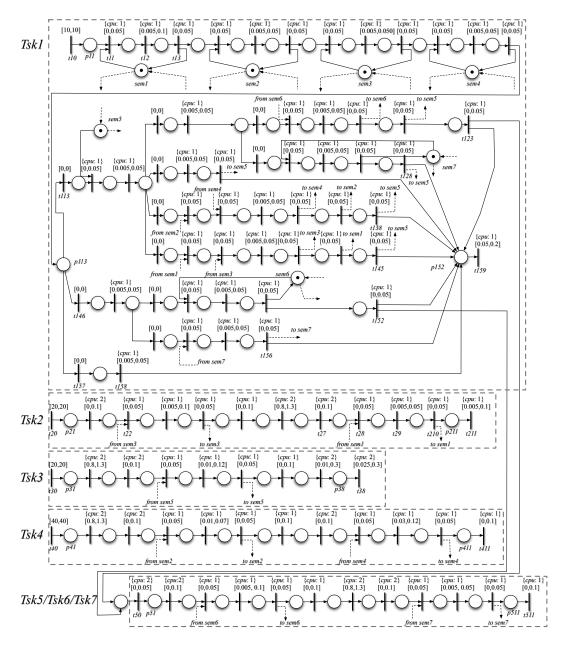

|    | 3.3                                         | Suppo                                             | rting development activities through pTPNs             | 50 |  |  |  |

|    |                                             | 3.3.1                                             | Formal specification                                   | 52 |  |  |  |

|    |                                             | 3.3.2                                             | Architectural verification                             | 56 |  |  |  |

|    |                                             | 3.3.3                                             | Disciplined implementation of real-time code           | 57 |  |  |  |

|    |                                             | 3.3.4                                             | Execution Time profiling                               | 58 |  |  |  |

| 4  | Implementing a tool to manage the ontology  |                                                   |                                                        |    |  |  |  |

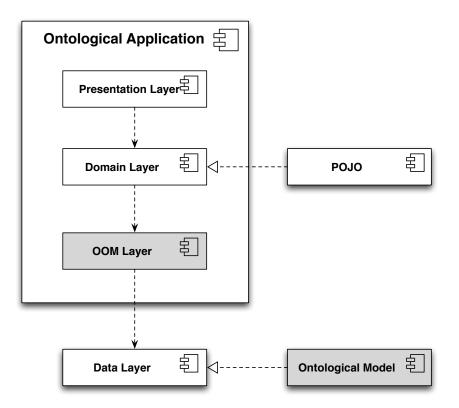

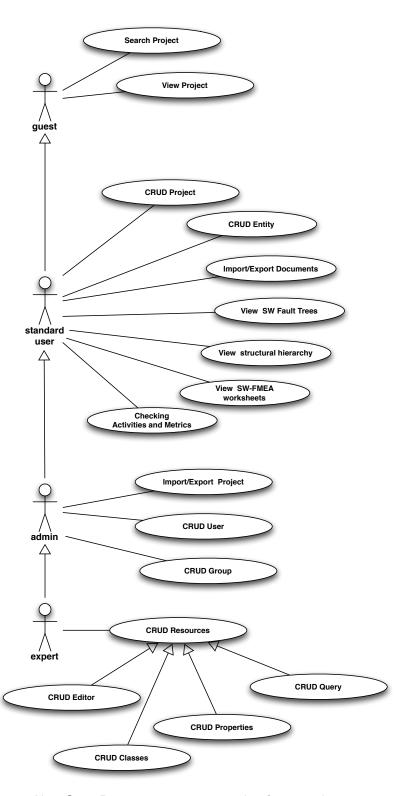

|    | 4.1                                         | Archite                                           | ecture and use cases                                   | 65 |  |  |  |

|    | 4.2                                         | Basic t                                           | tool capabilities                                      | 68 |  |  |  |

|    | 4.3                                         | Advanced tool capabilities                        |                                                        |    |  |  |  |

|    | 4.4                                         | Praction                                          | cal experimentation on a real case study               | 76 |  |  |  |

| Co | Conclusions                                 |                                                   |                                                        |    |  |  |  |

| Bi | Bibliography                                |                                                   |                                                        |    |  |  |  |

# List of Acronyms

AASTR APS Autonomous Star Tracker

**ADL** Architectural Description Language

**APS** Active Pixel Sensor

**ASD** Astrium Space Deutschland

**BCCT** Best Case Completion Time

**BDA** Bi-Directional Analysis

**CENELEC** European Committee for Electrotechnical Standardization

**CRC** Class Responsibility Collaboration

**CRUD** Create, Retrieve, Update, Delete

**CSCI** Computer Software Configuration Item

DAL Development Assurance Level

**DSML** Domain Specific Modeling Language

**ECSS** European Cooperation for Space Standardization

**ESA** European Space Agency

EU Electronic Unit

**FMEA** Failure Mode and Effects Analysis FT Fault Tree

FTA Fault Tree Analysis

GSPN Generalized Stochastic Petri Net

HCI Hardware Configuration Item

IEC International Electrotechnical Commission

IRC InfraRed Camera

ISO International Organization for Standardization

IT Image Tracking

LOC Lines Of Code

LQN Layered Queuing Network

LS Laser Sensor

MB Main Board

MCS Minimal Cut Set

MDD Model Driven Development

MIL-STD Military Standard

NMSPN Non-Markovian Stochastic Petri Net

OS Optical Sensor

OU Optical Unit

OWL Ontology Web Language

PA Process Algebra

PN Petri Net

POJO Plain Old Java Object

pTPN preemptive Time Petri Net

QN Queuing Network

QoS Quality of Service

RAMS Reliability, Availability, Maintainability and Safety

**RAMSES** Reliability Availability Maintainability and Safety

Engineering Semantics

**RDF** Resource Description Framework

**RTAI** Real Time Application Interface

**RTCA** Radio Technical Commission for Aeronautics

**RTOS** Real-Time Operating System

SC System Control

SD1 System Requirements Analysis

SD2 System Design

SD3 SW-HW Requirements Analysis

SD4-SW Preliminary Software Design

SD5-SW Detailed Software Design

SD6-SW SW Implementation

SD7-SW SW Integration

SD8 System Integration

SD9 Transition To Utilization

**SDD** Software Design Description

SIL Safety Integrity Level

SM Servo-Motor

SMU System Monitoring Unit

SPA Stochastic Process Algebra

**SPARQL** SPARQL Protocol and RDF Query Language SRS Software Requirements Specification

**SSDD** System/Subsystem Analysis and Design

**STD** Software Testing Description

SW software

Software Failure Mode and Effects Analysis **SW-FMEA**

SW-FTA Software Fault Tree Analysis

**SWRL** Semantic Web Rule Language

TE Top Event

**TPN** Time Petri Net

TS Temperature Sensor

**TVC** Tele Vision Camera

**UML** Unified Modeling Language

**UML-MARTE** UML profile for Modeling and Analysis of Real-Time and

Embedded systems

**UML-SPT** UML profile for Schedulability, Performance, and Time

**URI** Universal Resource Identifier

VΡ Video Processor

W3C World Wide Web Consortium

**WCCT** Worst Case Completion Time

**XML** Extensible Markup Language

# Introduction

In the life cycle of safety-critical systems, development and documentation activities comprise a major step of the overall effort. While intended to support quality assessment along the entire life cycle, they become crucial in a more evident manner at the time of certification.

In industrial environments, the development life cycle of safety-critical SW is subject to specific certification standards, such as RTCA/DO-178B-C [94] for airborne SW, MIL-STD-498 [112] for military devices, CENELEC EN 50128 [34] for railways signalling, ECSS E-40 [45] for space, and ISO/IEC 62304 [64] for medical devices. These standards prescribe to perform activities and to produce documents collecting information scattered all along the development life cycle. Nature and form of practices and artifacts required by different standards share many common principles, and basically refer to the common framework of the V-Model lifecycle [30, 39].

The inherent complexity of prescribed activities is largely exacerbated by their dependency on information relative to different stages of development. In particular, these data are formalized in different documentation artifacts, often contributed by different parties or units, and pertaining to three different perspectives: the structural elements of design and implementation, the functional and *Reliability, Availability, Maintainability and Safety* (RAMS) requirements, and the organization of the overall process. The integration of these three perspectives may largely improve the trade-off between reward and

effort spent in verification and quality-oriented activities, and it may open the way to agile tailoring of the process model to the specific characteristics of different projects and organizations.

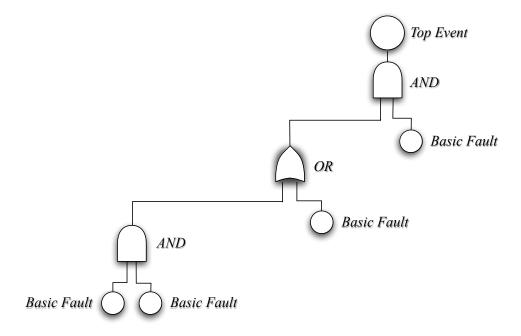

Among the activities prescribed by safety critical standards, Failure Mode and Effects Analysis (FMEA) and Fault Tree Analysis (FTA) aim at evaluating RAMS requirements, verifying the completeness of the countermeasures taken to mitigate the frequency of failures, by leveraging the analysis of the implemented functionalities and of the interactions among internal and external system components. More specifically, FMEA [73] is prescribed in industrial contexts to identify failure modes, their causes and effects, as well as determine actions reducing the impact of failure events. The analysis is carried out since the initial phases of the development process, when mitigating actions can be more easily taken. Unfortunately, FMEA-related information is usually acquired in natural language, implying that interpretation of the terms and concepts used across the analysis may differ from team to team; even the same team may give different interpretation when reusing an already performed analysis in a later occasion. Due to the lack of reusability, FMEA is often done from scratch. FMEA was first developed by the Department of Defence of USA and standardized in the MIL-STD-1629A [111], and it was then extended to various other industrial domains, some of which developed their own standards. FTA [119] is often carried out as the verification of FMEA. In fact, while FMEA is a bottom-up analysis, FTA is a top-down analysis that starts from a failure mode of the system and identifies conditions that would cause that failure mode. In other words, once a specific hazard is identified, FTA searches all possible combinations of the conditions that could force the system to reach the state of hazard.

Efficient and effective management of the volume and the heterogeneity of data involved in the development process have motivated research on methodologies for a systematic approach to execution, integration and correlation of all the activities performed during the product life cycle and of their relevant products (this whole concept is called *systematization*). The systematization of development practices may facilitate agile tailoring of the process model to

the specific characteristics of different projects and organizations, adapting to different constraints set by the applicable certification standards.

Ontological modelling and semantic technologies provide a relatively recent yet mature basis that may support this systematization aim. An ontology is defined as an explicit specification of a conceptualization [56], this means that it is used to formalize concepts involved in any domain of interest. In [51], three ontological models are proposed to characterize relations among components, functions, and quality attributes in complex embedded systems. The method and the system presented in [123] aim at facilitating reuse of knowledge as well as supporting complete and precise descriptions of processes and products. The semantic knowledge is hierarchically organized in form of taxonomies, containing typical recurring technical knowledge about systems, functions, failure modes, and actions. In [81], an ontology-based model-driven engineering process for compositional safety-analysis is introduced. The authors elaborate a domain ontology allowing the integration of a reasoner and inference rules to detect lack of model elements and inconsistent parts. In [41], the ontological formalization of FMEA concepts provides the ground for their explicit representation and for their unambiguous interpretation, while an ontology for the formalization of fault trees is proposed in [42]. In [70], a mapping from the concepts of an extended functional ontology to the concepts of a classic FMEA worksheet is introduced. The ontology presented in [16] enables to support the automation of activities and the management of information related to the FMEA process applied to SW (SW-FMEA), showing the effectiveness of the methodology in the context of a space project. Such ontological model is integrated with SW metrics in [15].

In this thesis, an ontological approach is proposed to support the development of safety-critical systems, also implementing a tool that enables its enactment in the framework of various certification standards. In particular, semantics of concepts and data involved in the development process is formalized, providing a common conceptual framework robust enough to enforce cohesion and consistency among information elements acquired along different phases of the development process and possibly contributed by dif-

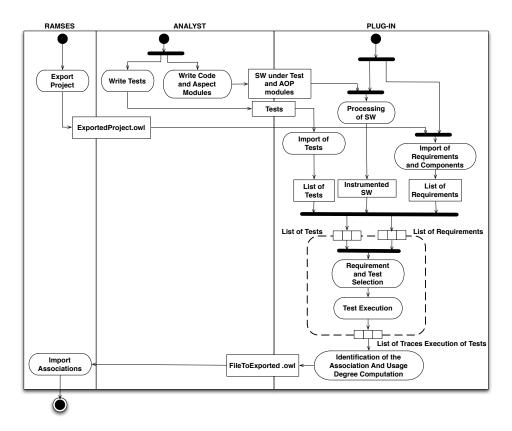

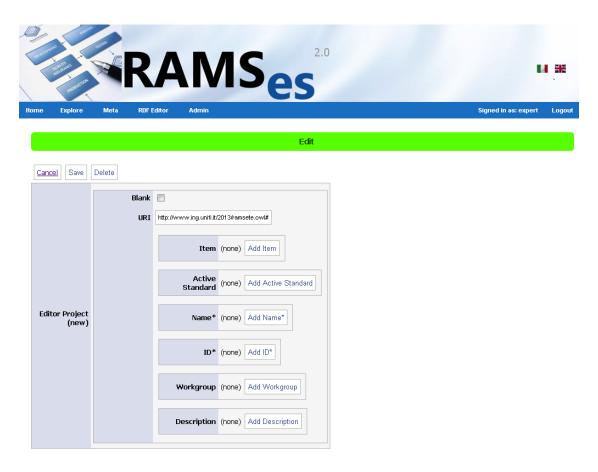

ferent parties. The ontological model presented in this dissertation provides a self-consistent representation of concepts involved in three different perspectives: i) the structural perspective concerned with the structural decomposition; ii) the functional perspective concerned with functional requirements and quality attributes; iii) the process perspective concerned with the phases of the development and the documents produced. The framework permits to attach a machine-readable semantics to concepts collected in the life cycle and to tailor the model to the characteristics of different standards leveraging the extensibility and the manageability provided by the ontological architecture. The enactment of the ontological model in a practical application context is shown from two different points of view. On the one hand, the UML profile for Modeling and Analysis of Real-Time and Embedded systems (UML-MARTE) diagrams [84] and the preemptive Time Petri Net (pTPN) theory [26] are combined both to manage the documentation process prescribed by MIL-STD-498 [112] and to support design and verification activities of the development process. On the other hand, the ontological model is directly cast into an advanced SW architecture, built on top of well-established Semantic Web technologies. The formalized conceptualization enables effective application of reasoning tools aiding the accomplishment of crucial and effort-expensive activities.

The rest of the thesis is organized as follows:

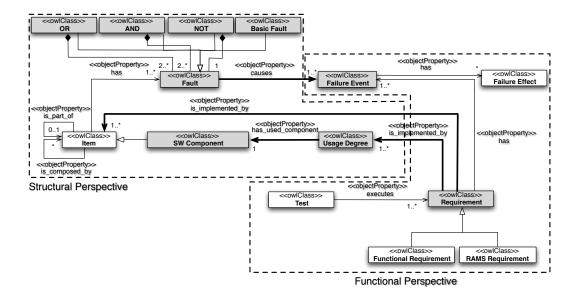

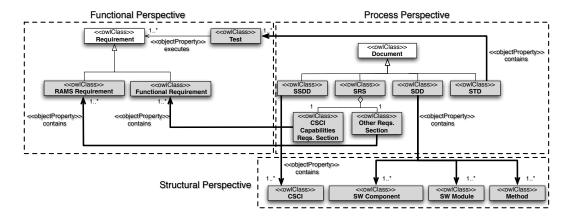

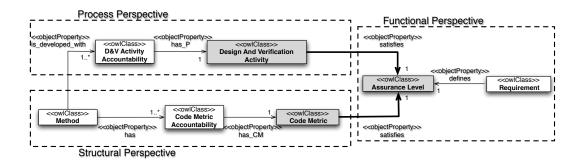

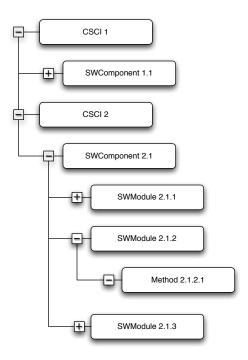

- Chapter 1 recalls features of ontologies and Semantic Web technologies (Section 1.1), then describes the intensional part of the ontological model, made up by concepts comprised in the structural, functional and process perspectives (Section 1.2). Finally, SW-FMEA and SW-FTA are addressed, highlighting concepts of the model that are involved in these two techniques (Section 1.3).

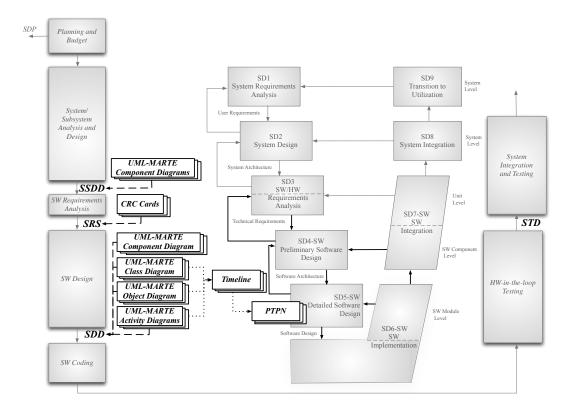

- Chapter 2 illustrates an industrial tailoring of the V-Model SW life cycle, specifying the documents produced in each development activity (Section 2.1), then it describes the population of the extensional part of the ontology, illustrating the associations between concepts which provide the connections among the three perspectives (Section 2.2).

- Chapter 3 describes the application of the methodology to a project of development, introducing the context of application (Section 3.1) and showing how the documentation process is managed with UML-MARTE diagrams (Section 3.2) and how the design and verification activities are supported by pTPN theory (Section 3.3).

- Chapter 4 illustrates the tool supporting the methodology, through its architecture and its usage (Section 4.1), its functionalities, from basic (Section 4.2) to advanced (Section 4.3), and through the experience done within the real scenario of a scheduler of an electromechanical system for immunoenzymatic analyses (Section 4.4).

# Chapter

# Defining an ontology to systematize life cycle activities

The aim of this thesis is to provide a methodology to support the development process of safety critical systems, systematizing activities and practices typical of industrial contexts. This is carried out through an ontological model and a tool that leverages Semantic Web techniques.

This Chapter gives a hint of ontologies and ontological architectures (Section 1.1), describes the ontological model representing concepts involved in the development process (Section 1.2), and explains how these concepts support SW-FMEA and SW-FTA (Section 1.3).

#### 1.1 **Ontologies**

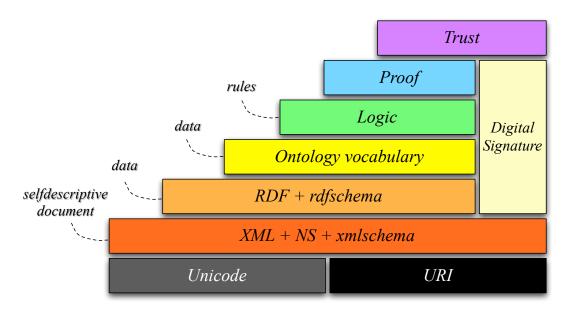

An *ontology* is an explicit and formal specification of a shared conceptualization [56]. Ontologies are technologies for knowledge representation and constitute one of the main elements of the Semantic Web [12]. For a better understanding, ontologies should be evaluated in the context of the stack of technologies and standards of the Semantic Web shown in Figure 1.1: Ontology Web Language (OWL) [77], the language standardized by World Wide Web Consortium (W3C) used to describe ontologies, depends on Resource Description Framework (RDF) [69] and RDF Schema [22] which, in turn, depend on Extensible Markup Language (XML) [21] and XML Schema [48]. Here only the main features needed to comprehend the proposed ontological architecture will be described.

Figure 1.1. Stack of the Semantic Web technologies.

#### 1.1.1 RDF ed RDF Schema

RDF [69] is the standard proposed by W3C for the encoding, the exchange, and the reuse of web metadata and is made up by two components: on the one hand the RDF Model and Syntax, which describes the structure of models and their representation in XML, on the other hand the RDF Schema, which describes the syntax needed to define schemas and vocabularies to represent metadata.

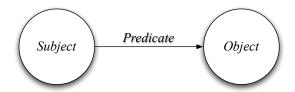

In a RDF model, every resource is identified by means of a *Universal Re*source Identifier (URI). The minimum unit which contains information is constituted by a *statement*, which is a triple of resources, shown in Figure 1.2, identified by a *subject*, a *predicate*, and an *object*. The object can be a datatype expression such as a string or a number as well as a resource.

Figure 1.2. The RDF triple.

A RDF model is constituted by some statements that can be connected by means of resources. The resource which represents the subject of a triple can be also, without any limitations, the object of another triple so as to construct an oriented graph. RDF models are extremely flexible because resources described in the models have not any special meaning. Only through RDF Schema a hierarchy of classes and a set of objects are defined through the specification of their meaning. RDF Schema is a vocabulary for describing properties and classes of RDF resources, together with semantics for generalization-hierarchies of such properties and classes.

#### Ontology Web Language 1.1.2

OWL [77] is the language proposed by W3C for the encoding of ontological models and is part of the stack of the technologies recommended for the Semantic Web. OWL is a vocabulary, which extends the vocabulary of RDF Schema, for the description of classes and properties of RDF Resources. Here only the main aspects of the language are described to give a compact and precise overview on its features and potentialities.

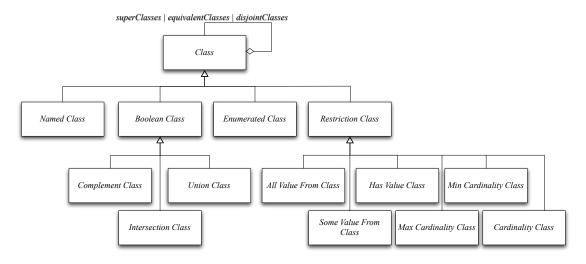

The fundamental elements of an ontological model are classes, which represent categories, sets or collections of elements (for example Doctor and Patient, but also Time and Space). Figure 1.3 shows how a class can be defined: through the specification of the name, using the notion of set, enumerating the elements which form the class, or applying a restriction on the value of a property. Classes can be related each other through inheritance, equivalence or disjointness.

Figure 1.3. Simplified model of classes in OWL.

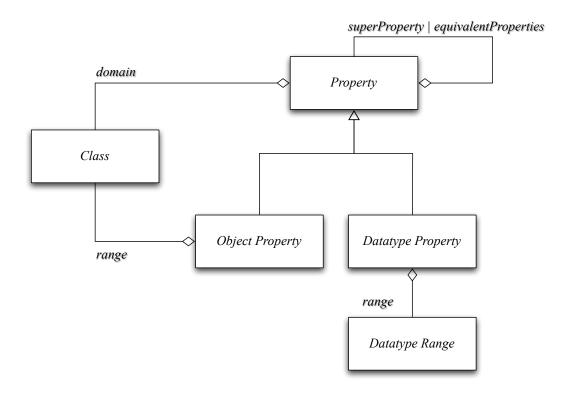

The other fundamental elements of ontological models are *properties*, which describe the internal structure of classes or the relations among classes. Figure 1.4 shows how properties and their features can be defined in OWL, for example they can be symmetric or transitive. Properties, such as classes, can be related each other through inheritance, equivalence or disjointness.

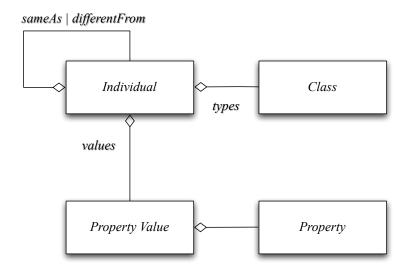

Classes and properties represent the *intensional* part of the ontology, while their instantiations represent the extensional part: individuals are realizations of concepts described by classes and attributes are realizations of properties.

The OWL language provides three increasingly expressive sublanguages designed for use by specific communities of implementers and users:

• OWL Lite supports those users primarily needing a classification hierarchy and simple constraint features. For example, it provides support for thesauri and other taxonomies.

Figure 1.4. Simplified model of properties in OWL.

Figure 1.5. Simplified model of individuals in OWL.

- OWL DL supports those users who want the maximum expressiveness without losing computational completeness (all entailments are guaranteed to be computed) and decidability (all computations will finish in finite time) of reasoning systems. OWL DL includes all OWL language constructs with restrictions such as type separation (a class can not also be an individual or property, a property can not also be an individual or class). OWL DL is so named due to its correspondence with Description Logics, a field of research that has studied a particular decidable fragment of first order logic. OWL DL was designed to support the existing Description Logic business segment and has desirable computational properties for reasoning systems.

- OWL Full is meant for users who want maximum expressiveness and the syntactic freedom of RDF with no computational guarantees. For example, in OWL Full a class can be treated simultaneously as a collection of individuals and as an individual in its own right.

Each of these sublanguages is an extension of its simpler predecessor, both in what can be legally expressed and in what can be validly concluded.

Recently, W3C has defined OWL 2 [120] which is an extension and revision of OWL, guaranteeing complete backwards compatibility with OWL 1. In fact, almost all the building blocks of OWL 2 were present in OWL 1, albeit possibly under different names.

#### SPARQL Protocol and RDF Query Language 1.1.3

SPARQL Protocol and RDF Query Language (SPARQL) [90] is a query language recommended for RDF by W3C. It can be used to express queries across diverse data sources, whether the data is stored natively as RDF or viewed as RDF via middleware. SPARQL contains capabilities for querying required and optional graph patterns along with their conjunctions and disjunctions. SPARQL also supports extensible value testing and constraining queries by source RDF graph. The results of SPARQL queries can be results sets or RDF graphs.

Most forms of SPARQL query contain a set of triple patterns called a basic graph pattern. Triple patterns are like RDF triples except that each of the subject, predicate and object may be a variable. A basic graph pattern matches a subgraph of the RDF data when RDF terms from that subgraph may be substituted for the variables and the result is RDF graph equivalent to the subgraph.

For example, Listing 1.1 shows a simple SPARQL query to find the title of a book from a graph of information. The query consists of two parts: the SELECT clause identifies the variables to appear in the query results, and the WHERE clause provides the basic graph pattern to match against the data graph. The basic graph pattern in this example consists of a single triple pattern with a single variable (?title) in the object position.

```

SELECT ?title

WHERE {

<http://example.org/book/book1> <http://example.org/title> ?title .

```

Listing 1.1. Example of a SPARQL query.

This query is supposed to be executed on the data graph shown in Listing 1.2.

```

<http://example.org/book/book1> <http://example.org/title> ''First example''

```

Listing 1.2. RDF model on which the SPARQL query is executed.

The result of the execution of the query is shown in Table 1.1.

```

title

"First Example"

```

Table 1.1. Result of the SPARQL guery.

#### Semantic Web Rule Language 1.1.4

Semantic Web Rule Language (SWRL) [59] is a language proposed by W3C for writing inference rules and is a combination of OWL-DL with the Rule Markup Language [19]. It extends the set of OWL axioms to include Horn-like rules. It thus enables Horn-like rules to be combined with an OWL knowledge base, allowing the application of deduction and inference rules on ontological models.

The proposed rules are of the form of an implication between an antecedent (body) and consequent (head). The intended meaning can be read as: whenever the conditions specified in the antecedent hold, then the conditions specified in the consequent must also hold.

Both the antecedent (body) and consequent (head) consist of zero or more atoms. An empty antecedent is treated as trivially true (i.e. satisfied by every interpretation), so the consequent must also be satisfied by every interpretation; an empty consequent is treated as trivially false (i.e. not satisfied by any interpretation), so the antecedent must also not be satisfied by any interpretation. Multiple atoms are treated as a conjunction.

For example, using this syntax the rule shown in Listing 1.3 asserts that the combination of the hasParent and hasBrother properties implies the hasUncle property. In the abstract syntax the rule corresponds to the expression shown in Listing 1.4. It is worth noting that some rules that can be written through SWRL correspond to axioms that can be defined directly through OWL.

```

hasParent(?x1,?x2) and hasBrother(?x2,?x3) -> hasUncle(?x1,?x3)

```

Listing 1.3. Example of a SWRL rule.

#### 1.1.5 Ontological architecture

Ontological technologies mainly originate with the intent to contribute to the realization of the Semantic Web [12]. This denotes an evolution of the current web, in which information is semantically defined so as to enable automated

```

Implies(

Antecedent(hasParent(I-variable(x1) I-variable(x2))

hasBrother(I-variable(x2) I-variable(x3)))

Consequent(hasUncle(I-variable(x1)I-variable(x3)))

```

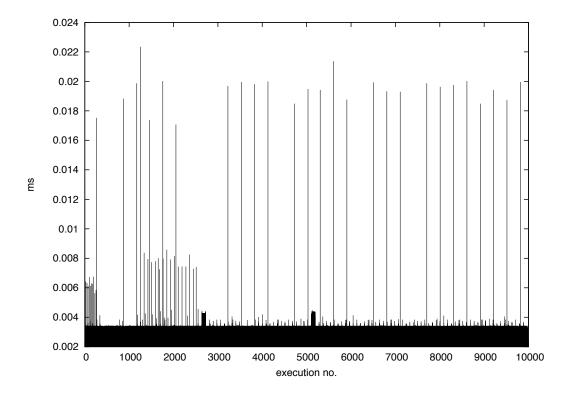

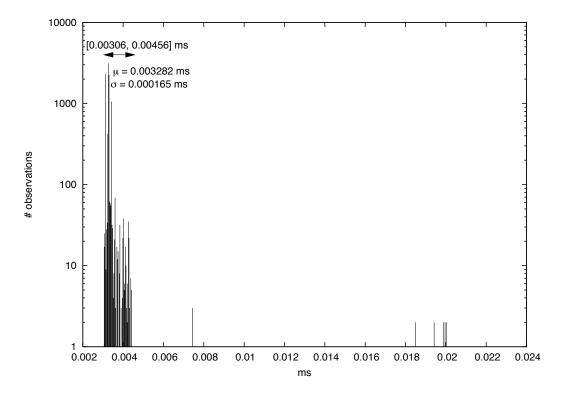

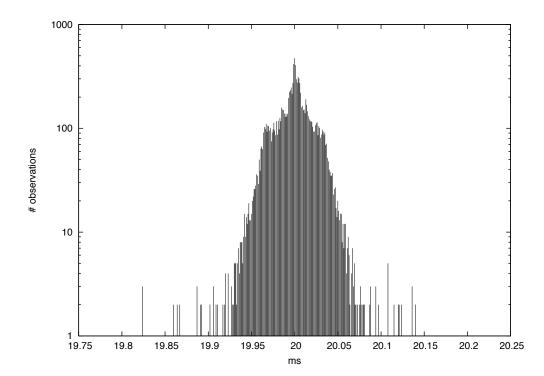

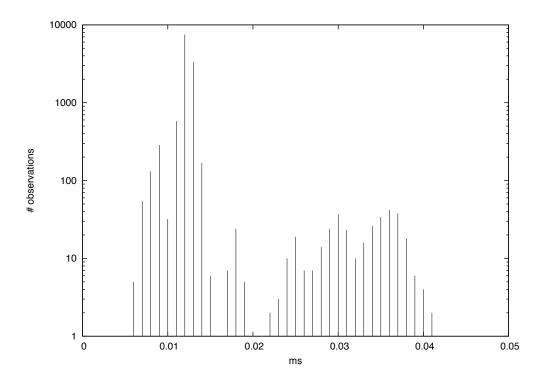

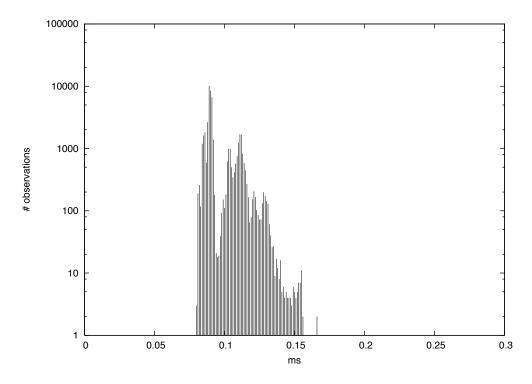

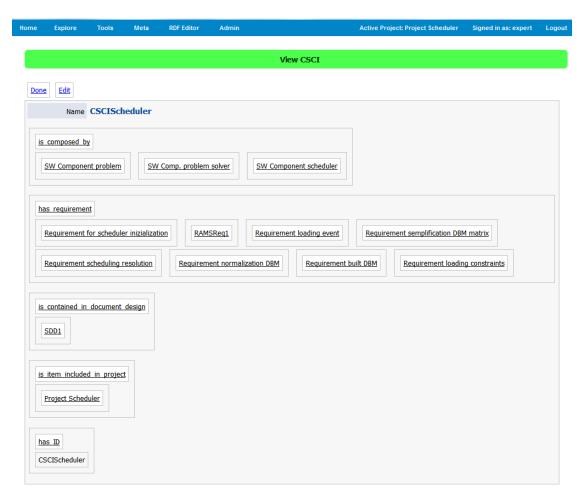

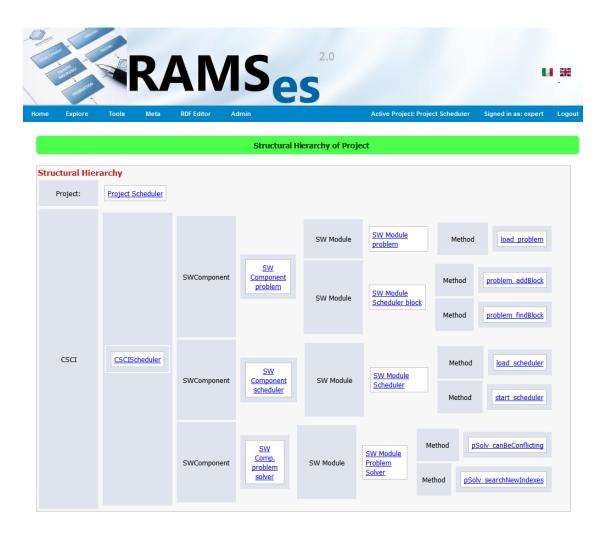

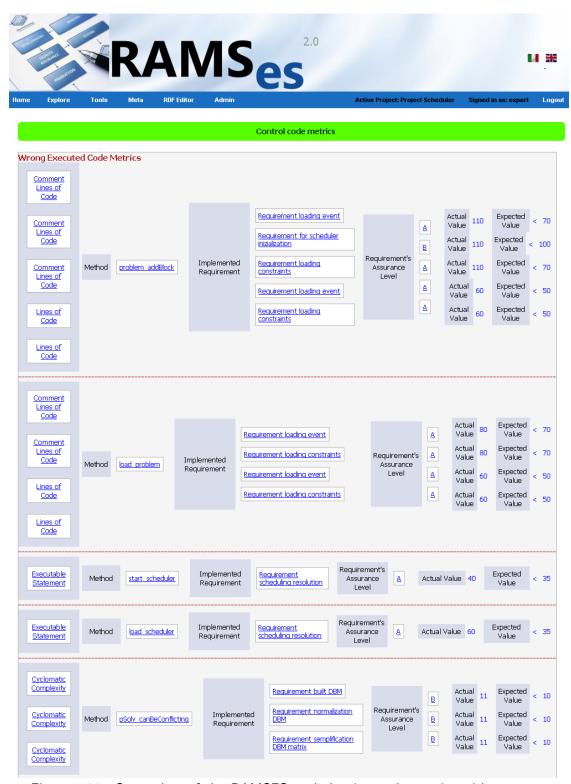

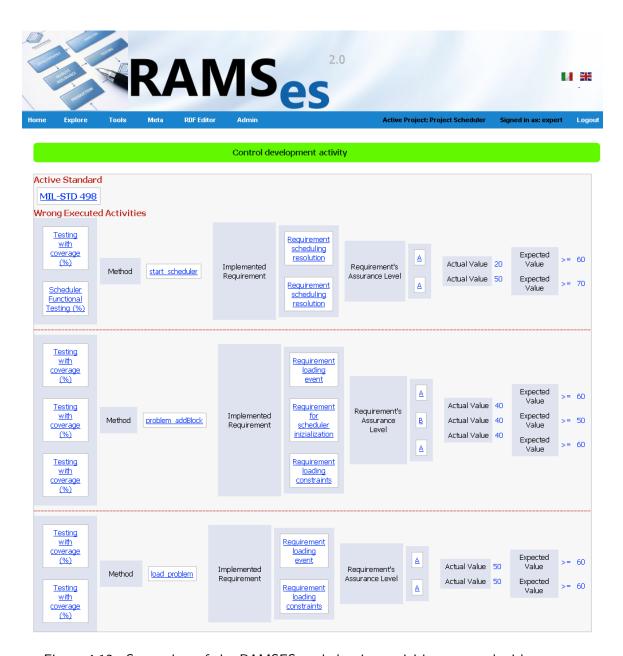

Listing 1.4. Example of a SWRL rule.