# Class E Full-Wave Low dv/dt Rectifier

Alberto Reatti, Member, IEEE, Marian K. Kazimierczuk, Senior Member, IEEE, and Richard Redl, Senior Member, IEEE

Abstract - An analysis and experimental verification for a Class E full-wave current-driven low dv/dt rectifier are given. Basic parameters of the circuit are derived using the timedomain analysis and Fourier series techniques. The rectifier diodes turn on and off at low dv/dt, yielding low switching noise and low switching losses. Diode parasitic capacitances do not adversely affect the circuit operation. The absolute value of di/dt is limited at diode turn-off, significantly reducing the reverse recovery current. The rectifier input voltage waveform differs only slightly from an ideal sinusoid, resulting in a low total harmonic distortion. The circuit has theoretically zero-ripple voltage and, therefore, zero loss in the equivalent series resistance (ESR) of the filter capacitor. The Class E full-wave topology has lower diode conduction loss than the Class E half-wave rectifier. The efficiency is almost constant over the load range from 10% to 100% of the full load. The rectifier offers high-power density, high-frequency rectification and is suitable for low-voltage and high-current applications, as shown by experimental results given for a 75 W rectifier which was operated at 1 MHz with an output of 5 V and 15 A. The theoretical and the experimental results were in good agreement.

#### I. INTRODUCTION

CLASS E rectifiers are suitable for high-frequency, high-efficiency, and low-noise rectification [1]–[8]. In Class E current-driven half-wave rectifiers, the diode turns on at low dv/dt and turns off at low dv/dt and limited di/dt [3], resulting in low noise and switching losses. Moreover, the diode parasitic capacitances do not adversely affect the circuit operation because they are absorbed into capacitors connected in parallel with the diodes. The combination of a Class E rectifier with a Class E inverter yields dc–dc converters operating with narrow-band frequency regulation over the entire load range [9]–[22]. Unfortunately, conduction losses are the main limitation for Class E half-wave rectifier applications in converters with high-current and low-voltage outputs.

The purpose of this paper is to present an analysis and the experimental results of a Class E full-wave current-driven low dv/dt rectifier. This circuit has lower conduction loss in the diodes and in the parallel capacitors than the Class E half-wave topology. The ac component of the output current is theoretically zero, resulting in zero losses in the filter capacitor ESR. Actually, the filter capacitor loss is about 40 times less than in conventional peak rectifiers and 100 times lower than in Class

Manuscript received August 13, 1992; revised December 29, 1992. This work was supported by the National Science Foundation under Grant ECS-8922695. This paper was recommended by Associate Editor J. Choma, Jr.

A. Reatti is with the Department of Electronic Engineering, University of Florence, 50139 Florence, Italy.

M. K. Kazimierczuk is with the Department of Electrical Engineering, Wright State University, Dayton, OH 45435.

R. Redl is with ELFI S.A., Switzerland.

IEEE Log Number 9207936.

E half-wave rectifiers. The efficiency is almost constant over 90% of the entire load range. Another important advantage of the Class E full-wave rectifier is that the input voltage waveform only slightly differs from a sinusoid, resulting in a low THD circuit. Finally, the rectifier acts as an impedance inverter and, therefore, it is fully compatible with Class E inverters [9]–[19]. Because of these features, the Class E full-wave rectifier is suitable for high-frequency, high power-density applications, particularly, when a low output voltage and a high load current are required, e.g., 5 V or 12 V with the output power above 50 W [17]–[22].

The rectifier description and the principle of circuit operation are given in Section II. Section III contains the time-domain analysis and design equations for steady-state operation. Section IV presents a design example. Experimental results are given in Section V. Section VI contains the final conclusions. Derivations of the circuit characteristics are included in the Appendix.

## II. OPERATION OF THE RECTIFIER

## A. Circuit Description

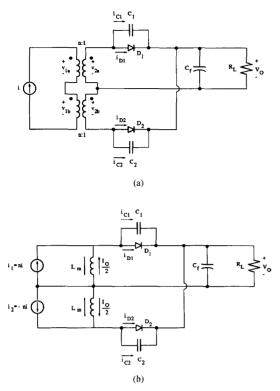

A circuit of a Class E full-wave current-driven low dv/dtrectifier [3], [22] is shown in Fig. 1(a). It consists of two diodes  $D_1$  and  $D_2$ , two capacitors  $C_1$  and  $C_2$  with the same capacitance C, a single-pole low-pass output filter  $C_f-R_L$ , and two transformers with a turns ratio n. Resistor  $R_L$  is a dc load. An equivalent circuit of the rectifier is shown in Fig. 1(b).  $L_m$  represents magnetizing inductances of the secondary windings of the transformers. It is assumed that they are equal and large enough to carry only a dc current and, therefore, can be considered as an open circuit for the ac component of the current. The leakage inductances, the core and the windings resistances, and the transformer stray capacitances are neglected. The diode parasitic capacitances are absorbed into capacitances  $C_1$  and  $C_2$  connected in parallel with the diodes. The ac component of the current flowing into the  $C_{f}$ - $R_{L}$  circuit is ideally zero, resulting in a constant zeroripple output voltage  $V_O$ . Actually, this is obtained with a small capacitor  $C_f$ .

## B. Principle of Operation

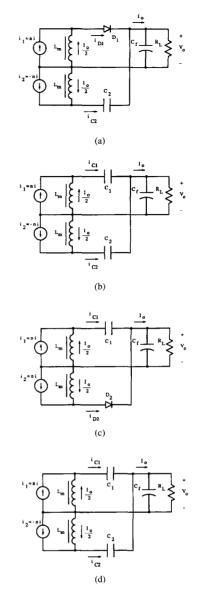

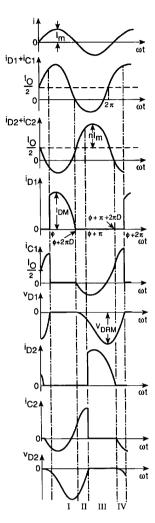

Fig. 2 shows four topological modes that the rectifier goes through during one switching period, when the maximum onduty cycle is lower than 0.5. Idealized current and voltage waveforms of the rectifier are depicted in Fig. 3. The input current i is sinusoidal with frequency  $f = \omega/2\pi$  and amplitude  $I_m$ . Consequently, currents  $i_1 = ni$  and  $i_2 = -ni$  are

1057-7122/92\$03.00 © 1992 IEEE

Fig. 1. Class E, full-wave current-driven, low dv/dt rectifier. (a) Circuit. (b) Model of the rectifier.

also sinusoidal. Since inductances  $L_m$  are equal, the current through each of them is  $I_O/2$ . As a result, the waveforms of the current through the parallel combinations of  $C_1$ – $D_1$  and  $C_2$ – $D_2$  are two sine waves that are  $180^{\circ}$  out of phase and both are shifted upward by dc component  $I_O/2$ . These waveforms are  $i_{C1}+i_{D1}=I_O/2+ni$  and  $i_{C2}+i_{D2}=I_O/2-ni$ , respectively. Since the current through the circuit  $C_f$ – $R_L$  is given by  $i_{C1}+i_{D1}+i_{C2}+i_{D2}$ , the resulting ac component of the current is zero. Therefore, the output has ideally zero-voltage ripple, even without the filter capacitor  $C_f$ . Actually, the capacitor  $C_f$  is much smaller than in conventional rectifiers circuit and its ESR produces low losses because the current through it has a low rms value.

The first topological mode of Fig. 2(a) begins at  $\omega t = \phi$ , when diode voltage  $v_{D1}$  reaches the diode threshold voltage, turning on diode  $D_1$ . During this phase, the current  $I_O/2 + nI_m sin\omega t$  flows through  $D_1$ . Diode  $D_2$  is off and its voltage waveform is shaped by the shunt capacitor  $C_2$ , according to  $i_{C2} = C_2 dv_{C2}/dt$ . The first mode ends at  $\omega t = \phi + 2\pi D$ , when current  $i_{D1}$  reaches zero, turning diode  $D_1$  off.

The second topological mode of Fig. 2(b) begins at  $\omega t = \phi + 2\pi D$ . During this time interval, the current  $I_O/2 + nI_m sin\omega t$  flows through  $C_1$  which shapes the waveform of the voltage across  $D_1$ , according to  $i_{C1} = C_1 dv_{C1}/dt$ . Since the capacitor current is zero when diode  $D_1$  turns off, the derivative of the voltage waveform  $v_{D1}$  is also zero at  $\omega t = \phi + 2\pi D$ . After diode  $D_1$  turns-off, its voltage slowly decreases because  $i_{C1}$  is negative. Since  $i_{C2}$  is positive, the

Fig. 2. Models of Class E, full-wave current-driven, low dv/dt rectifier for various time intervals. (a) Model with  $D_1$  ON and  $D_2$  OFF (b) Model with  $D_1$  OFF and  $D_2$  OFF, (c) Model with  $D_1$  OFF and  $D_2$  ON. (d) Model with  $D_1$  OFF and  $D_2$  OFF.

voltage  $v_{D2}$  increases and reaches the diode threshold voltage at  $\omega t = \phi + \pi$ , turning on diode  $D_2$ .

The third topological mode of Fig. 2(c) begins at  $\omega t = \phi + \pi$ , when diode  $D_2$  turns on and ends at  $\omega t = \phi + \pi + 2\pi D$ , when it turns off. During this time interval, the current  $I_O/2 - nI_m sin\omega t$  flows through diode  $D_2$ . The waveform of the voltage across diode  $D_1$  is still shaped by  $C_1$ . Therefore, it first decreases, reaches its minimum value  $V_{DRM}$  when  $i_{C1}$  is zero, and then increases when  $i_{C1}$  is positive.

The fourth mode of Fig. 2(d) begins, when the current  $i_{D2}$  reaches zero. As in the first topological mode,  $C_2$  shapes the voltage waveform of  $D_2$ . Hence,  $v_{D2}$  slowly decreases from

Fig. 3. Current and voltage waveforms in the Class E full-wave rectifier.

zero because  $i_{C2}$  is zero at  $\omega t = \phi + \pi + 2\pi D$ . The current through capacitor  $C_1$  is positive and, therefore, voltage  $v_{D1}$  increases. Diode  $D_1$  turns on at  $\omega t = \phi + 2\pi$ , when  $v_{D1}$  reaches the threshold voltage. This ends the fourth topological mode and the entire switching cycle.

The symmetrical behavior of the rectifier is demonstrated by the current and voltage waveforms of Fig. 3 because the waveforms of  $i_{D1}$  and  $v_{D1}$  and those of  $i_{D2}$  and  $v_{D2}$  are equal and 180° out of phase.

The rectifier circuit takes advantage of the externally connected capacitances  $C_1$  and  $C_2$  because they shape the voltage across the diodes when the diodes are off. They also absorb the diode parasitic capacitances and, therefore, these capacitances do not adversely affect the circuit operation. The diodes turn off at zero dv/dt=0 and turn on at a limited dv/dt. As a result, the current through the parasitic capacitances of the diodes is reduced at both transitions. The current source limits the value of di/dt when the diodes turn off. Therefore, the detrimental effect of the reverse-recovery charge is significantly reduced, if

pn junction diodes are used. The limited value of dv/dt at both transitions and the limited value of di/dt at the turn-off reduce the level of noise produced by the rectifier and switching losses in the diodes. Current and voltage waveforms of each diode do not overlap during either transition and thus yield low switching losses. Another important advantage of the rectifier is that it has theoretically zero-ripple output-voltage. This is because the ac components of the diode and capacitor currents flowing into the  $C_f{-}R_L$  circuit are equal in magnitude and shifted in phase by  $180^{\circ}$ . The circuit is called a Class E rectifier because current and voltage waveforms in each side of the rectifier are mirror images of the corresponding waveforms in the Class E zero-voltage switching amplifiers [9].

#### III. ANALYSIS

The analysis of the Class E rectifier of Fig. 1(a) begins with the following assumptions:

- The diodes are ideal, i.e., they have zero threshold voltage, zero on-resistance, infinite off-resistance, and zero minority carrier charge lifetime in the case of the pn junction diode.

- 2) The on-duty cycle  $D_{max}$  of each diode is equal to or less than 50%.

- 3) The  $C_f$ - $R_L$  circuit can be replaced by a dc voltage source.

- The rectifier is driven by an ideal sinusoidal current source, described by

$$i = I_m sin\omega t \tag{1}$$

where  $I_m$  is the amplitude and  $\omega = 2\pi f$  is the angular frequency.

5) The transformers are ideal and have a turns ratio of n and secondary magnetizing inductances  $L_m$ . The leakage inductances, the winding and core resistances, and the stray capacitances of the transformers are ignored. The magnetizing inductances are assumed to be identical and large enough so that they represent an open circuit for the ac component of the current flowing through the parallel combination of the diode and capacitor.

All derivations are included in the Appendix and only final results are given subsequently. Diode  $D_1$  turn-on delay angle is given by

$$tan\phi = -\frac{\pi(1-D)sin(2\pi D) + sin^2(\pi D)}{\pi(1-D)cos(2\pi D) + sin(\pi D)cos(\pi D)}.$$

(2)

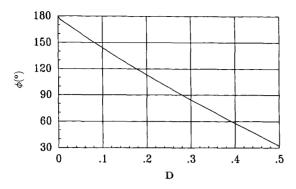

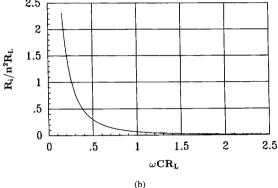

Fig. 4 shows a plot of  $\phi$  as a function of D. The phase  $\phi$  decreases from  $180^{\circ}$  to  $30^{\circ}$  while D decreases from 0.5 to 0. This means that the shorter the duty cycle, the higher the delay angle corresponding to the diode turn-on. Also, the current through the diodes becomes more and more impulsive with a decreasing on-duty cycle. Because of the symmetrical behavior of the circuit, the diode  $D_2$  turn-on delay angle is  $\phi + \pi$  and its on-duty cycle is D.

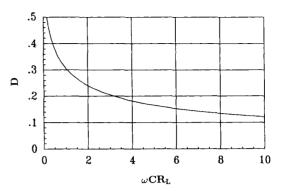

Fig. 5 shows the diode on-duty cycle D as a function of the load resistance  $R_L$  normalized with respect to the reactance

Fig. 4. Initial phase of the input voltage  $\phi$  as a function of the diode ON duty cycle D.

of each parallel capacitor  $1/\omega C$

$$\omega CR_{L} = \frac{\sin(\phi + 2\pi D) - \sin\phi + 2\pi (1 - D)\cos(\phi + 2\pi D)}{4\pi \sin(\phi + 2\pi D)} - \frac{\pi}{2} (1 - D)^{2}.$$

(3)

The duty cycle decreases from 0.5 to 0 when  $\omega CR_L$  is increased from  $(\omega CR_L)_{min}=0.1756$  to  $\infty$ . With a constant value of  $V_O$  and an increasing  $R_L$ , the output current  $I_O$  decreases and so does the current through the parallel combination of the diode and capacitor, causing the on–duty cycle D to decrease. The amplitude of the sinusoidal input current is

$$I_m = \frac{-I_O}{2nsin(\phi + 2\pi D)}. (4)$$

Hence, the waveforms of the currents through diodes  $D_1$  and  $D_2$ , normalized with respect to the dc output current  $I_O$ , are given by

$$\frac{i_{D1}}{I_O} = \begin{cases} \frac{1}{2} \left[ 1 - \frac{\sin\omega t}{\sin(\phi + 2\pi D)} \right], & \text{for } \phi \le \omega t < \phi + 2\pi D \\ 0, & \text{for } \phi + 2\pi D \le \omega t < \phi + 2\pi \end{cases}$$

and

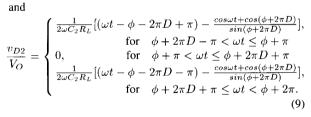

$$\frac{i_{D2}}{I_O} = \begin{cases}

0, & \text{for } \phi + 2\pi D - \pi \le \omega t < \phi + \pi \\ \frac{1}{2} \left[ 1 + \frac{sin\omega t}{sin(\phi + 2\pi D)} \right], & \text{for } \phi + \pi \le \omega t < \phi + \pi + 2\pi D \\ 0, & \text{for } \phi + 2\pi D + \pi \le \omega t < \phi + 2\pi. \end{cases}$$

(6)

The maximum value of  $i_{D1}$  occurs at  $\omega t = \pi/2$ , if  $\phi \leq \pi/2$ . However,  $\phi = \pi/2$  represents a boundary condition. When  $\phi$  is greater than  $\pi/2$ , the maximum of  $i_{D1}$  is not given by  $di_{D1}/dt = 0$ , but occurs at  $\omega t = \phi$ . Since the rectifier behavior is symmetrical, the peak currents are the same for  $D_1$  and  $D_2$  and are

$$\frac{I_{DM}}{I_O} = \begin{cases} \frac{1}{2} \left[ 1 - \frac{1}{\sin(\phi + 2\pi D)} \right], & \text{for } \phi \le \pi/2 & (D \ge 0.28) \\ \frac{1}{2} \left[ 1 - \frac{\sin\phi}{\sin(\phi + 2\pi D)} \right], & \text{for } \phi > \pi/2 & (D < 0.28). \end{cases}$$

(7)

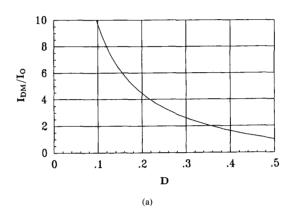

The peak value of the current normalized with respect to the output current  $I_{DM}/I_O$  is shown in Fig. 6(a) as a function of

Fig. 5. Diode ON duty ratio D as a function of normalizedload resistance  $\omega CR_I$ .

Fig. 6. Normalized peak values of diode current  $I_{DM}/I_O$  as functions of D and  $\omega CR_L$ . (a)  $I_{DM}/I_O$  versus D. (b) $I_{DM}/I_O$  versus  $\omega CR_L$ .

D. Its value increases when D decreases. Using (3), the ratio  $I_{DM}/I_O$  is plotted versus  $\omega CR_L$  in Fig. 6 (b).

The voltages across diodes  $D_1$  and  $D_2$ , normalized with respect to the output voltage  $V_O$ , are given by

$$\frac{v_{D1}}{V_O} = \begin{cases} 0, & \text{for } \phi < \omega t \leq \phi + 2\pi D \\ \frac{1}{2\omega C_1 R_L} [(\omega t - \phi - 2\pi D) + \frac{\cos \omega t - \cos(\phi + 2\pi D)}{\sin(\phi + 2\pi D)}], & \text{for } \phi + 2\pi D < \omega t \leq \phi + 2\pi \end{cases}$$

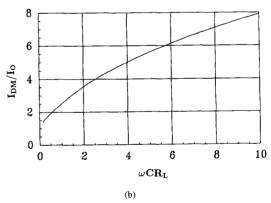

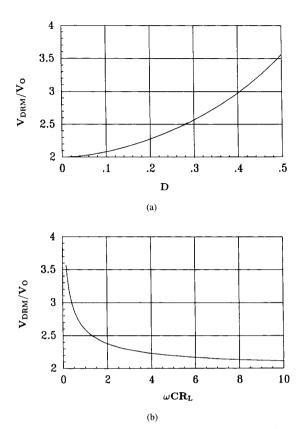

Fig. 7. Normalized peak values of diode reverse voltage  $V_{DRM}/V_O$  as functions of D and  $\omega CR_L$ . (a)  $V_{DRM}/V_O$  versus D. (b)  $V_{DRM}/V_O$  versus  $\omega CR_L$ .

The reverse voltage across diode  $D_1$  reaches the peak value when the current through  $C_1$  is zero, i.e., at  $\omega t = 3\pi - \phi - 2\pi D$ . Substituting this value of  $\omega t$  into (8), the normalized peak voltage across diode can be determined

$$\frac{V_{DRM}}{V_O} = \frac{1}{\omega CR_L} \left[ \frac{3\pi}{2} - \phi - 2\pi D - \cot(\phi + 2\pi D) \right]. \quad (10)$$

Using (2), (3), and (10), the normalized peak reverse voltage of the diodes can be plotted as functions of D and  $\omega CR_L$  as shown in Fig. 7(a) and (b), respectively.

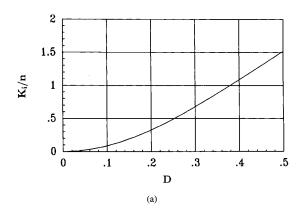

The normalized power-output capability is

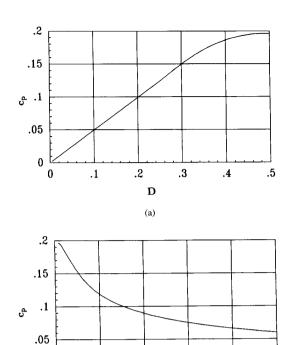

$$c_p = \frac{I_O V_O}{I_{DM} V_{DRM}}. (11)$$

Using (2) and (3), the factor  $c_p$  was computed and plotted versus D and  $\omega CR_L$  in Fig. 8(a) and (b), respectively. The maximum value of  $c_p$  occurs at D=0.5.

(b) Fig. 8. Power-output power capability  $c_p$  as functions of D and  $\omega CR_L$ . (a)  $c_p$  versus D. (b)  $c_p$  versus  $\omega CR_L$ .

4

6

$\omega CR_L$

8

10

2

0

The sinusoidal current source driving the rectifier can actually be obtained using any power inverter with a series-resonant circuit. Hence, the equivalent input impedance of the rectifier at the fundamental frequency must be determined. It can be represented by a series connection of a resistance  $R_i$  and a capacitance  $C_i$ . The component of the input voltage  $v_i$  in phase with the input current i has the amplitude expressed by

$$V_{Rim} = \frac{nV_O}{\pi\omega CR_L} [sin\phi - sin(\phi + 2\pi D) + \pi cos(\phi + 2\pi D) + (2\pi D - \pi)cos\phi + \frac{cos\phi - cos(\phi + 2\pi D)}{tan(\phi + 2\pi D)} + \frac{cos2(\phi + 2\pi D) - cos2\phi}{4sin(\phi + 2\pi D)}].$$

(12)

Substitution of (4) and (12) into  $R_i = V_{Rim}/I_m$  gives the rectifier input resistance

$$R_{i} = \frac{2n^{2}sin(\phi + 2\pi D)}{\pi\omega C} [sin(\phi + 2\pi D) - sin\phi$$

$$-\pi cos(\phi + 2\pi D) - (2\pi D - \pi)cos\phi$$

$$-(cos\phi - cos(\phi + 2\pi D))cot(\phi + 2\pi D)$$

$$-\frac{cos2(\phi + 2\pi D) - cos2\phi}{4sin(\phi + 2\pi D)}]. \tag{13}$$

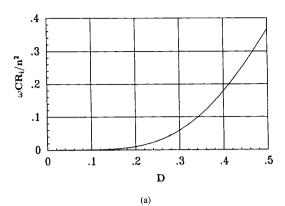

Using (2) and (3), both  $R_i/n^2R_L$  and  $\omega CR_i/n^2$  are plotted as functions of D and  $\omega CR_L$  in Fig. 9 and 10, respectively.

Fig. 9. Normalized input resistance  $R_i/n^2R_L$  as functions of D and  $\omega CR_L$ . (a)  $R_i/n^2R_L$  versus D. (b)  $R_i/n^2R_L$  versus  $\omega CR_L$ .

The component of the input voltage which is 90° out of phase with respect to the input current i has the amplitude

$$V_{Cim} = \frac{nV_O}{\pi \omega C R_L} [\cos\phi + (\pi - 2\pi D)\sin\phi - \cot(\phi + 2\pi D)\sin\phi - \pi\sin(\phi + 2\pi D) + \frac{2(\pi D - \pi)}{\sin(\phi + 2\pi D)} - \frac{\cos(\phi + 2\pi D)}{2} + \frac{\sin\phi\cos\phi}{2\sin(\phi + 2\pi D)}]. \tag{14}$$

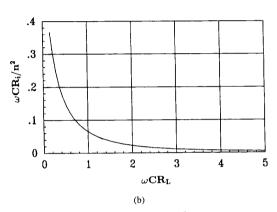

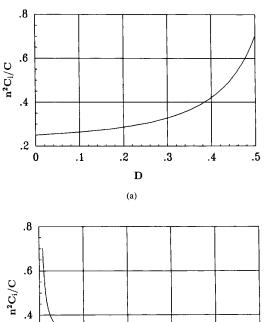

Since  $\omega C_i = I_m/V_{Cim}$ , (4) and (14) give the rectifier input capacitance  $C_i$  normalized with respect to the parallel capacitance C

$$\frac{C_i}{C} = \frac{\pi}{2n^2 sin(\phi + 2\pi D)} [cos\phi + (\pi - 2\pi D)sin\phi \\

- cot(\phi + 2\pi D)sin\phi - \pi sin(\phi + 2\pi D) \\

+ \frac{2(\pi - \pi D)}{sin(\phi + 2\pi D)} - \frac{cos(\phi + 2\pi D)}{2} \\

+ \frac{sin\phi cos\phi}{2sin(\phi + 2\pi D)}]^{-1}.$$

(15)

Substituting (2) and (3) into (15),  $C_i/C$  is expressed as functions of D and  $\omega CR_L$ . Fig. 11(a) and (b) show the plots of the normalized input capacitance  $n^2C_i/C$  versus D and  $\omega CR_L$ , respectively.

Fig. 10. Normalized input resistance  $\omega_r C R_i / n^2$  as functions of D and  $\omega CR_L$ . (a)  $\omega_r CR_i/n^2$  versus D. (b)  $\omega_r CR_i/n^2$  versus  $\omega CR_L$

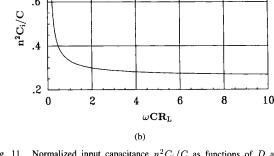

The ac-to-dc current transfer function is given by

$$K_i = \frac{I_O}{I_{rms}} = -2n\sqrt{2}sin(\phi + 2\pi D)$$

(16)

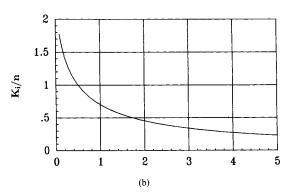

where  $I_{rms} = I_m/\sqrt{2}$ . The current transfer function  $K_i/n$  is plotted as functions of D and  $\omega CR_L$  in Fig. 12(a) and (b), respectively.

The ac-to-dc voltage transfer function is

$$M_R = \frac{V_O}{V_{1rms}} = \frac{V_O}{n} \sqrt{\frac{2n^2}{V_{Rim}^2 + V_{Cim}^2}}$$

(17)

where  $V_{1rms} = \sqrt{(V_{Rim}^2 + V_{Cim}^2)/2}$  is the rms value of the fundamental of the rectifier input voltage. Using (2) and (3), the ac-to-dc voltage transfer function  $nM_R$  is plotted in Fig. 13 (a) and (b) as functions of D and  $\omega CR_L$ , respectively.

The rectifier transconductance is

$$G_R = \frac{I_{rms}}{V_O} = \frac{-1}{R_L 2\sqrt{2}nsin(\phi + 2\pi D)}.$$

(18)

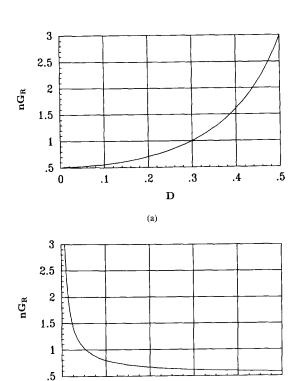

Substituting (2) and (3) into (18), the transconductance  $nG_R$ is plotted in Fig.14(a) and (b) as functions of D and  $\omega CR_L$ , respectively.

The conduction loss in each diode is

$$P_D = \frac{P_O}{2} \bigg\{ \frac{V_F}{V_O} + \frac{r_F}{2R_L} \bigg[ D + \frac{2\pi D + sin\phi cos\phi}{4\pi sin^2(\phi + 2\pi D)} \label{eq:power}$$

Fig. 11. Normalized input capacitance  $n^2C_i/C$  as functions of D and  $\omega CR_L$ . (a)  $n^2C_i/C$  versusD. (b)  $n^2C_i/C$  versus  $\omega CR_L$ .

$$+\frac{3}{4\pi tan(\phi+2\pi D)}-\frac{cos\phi}{\pi sin(\phi+2\pi D)}\Biggr]\Biggr\} \quad (19)$$

where  $V_F$  is the diode threshold voltage and  $r_F$  is the diode forward resistance. The loss in each parallel capacitor is

$$P_{C} = P_{O} \frac{r_{ESR}}{4R_{L}} \left[ 1 - D + \frac{2\pi(1-D) - sin\phi cos\phi}{4\pi sin^{2}(\phi + 2\pi D)} - \frac{3}{4\pi tan(\phi + 2\pi D)} + \frac{cos\phi}{\pi sin(\phi + 2\pi D)} \right]$$

(20)

where  $r_{ESR}$  is the ERS of the parallel capacitor. The power loss in the ESR of the filter capacitor is ideally zero. The rectifier efficiency is

$$\eta_R = \frac{P_O}{P_O + 2P_D + 2P_C}. (21)$$

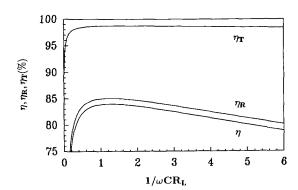

The rectifier efficiency  $\eta_R$  is plotted in Fig. 15 as a function of the normalized load conductance  $1/\omega CR_L$  for  $V_F=0.3$  V,  $r_F=0.033~\Omega$ , and  $r_{ESR}=0.04~\Omega$ . With this choice of the horizontal axis, the efficiency was easily plotted over the entire load range, that is, from no-load to full load. Note that the rectifier efficiency is almost constant for the load ranging from 10% to 100% of the full load.

The losses in the transformer windings are expressed by

$$P_{Cu} = (r_{w1} + n^2 r_{w2}) \frac{I_O^2}{8n^2 sin^2(\phi + 2\pi D)}$$

(22)

Fig. 12. Current transfer function  $K_i/n$  as functions of D and  $\omega CR_L$ . (a)  $K_i/n$  versus D. (b)  $K_i/n$  versus  $\omega CR_L$ .

where  $r_{w1}$  and  $r_{w2}$  are the resistances of the primary and secondary windings, respectively. The efficiency of the transformers is

$$\eta_T = \frac{1}{1 + \frac{P_{Cu}}{P_O + 2P_C + 2P_D}}. (23)$$

The efficiency of the transformers  $\eta_T$  is plotted in Fig. 15 as a function of the rectifier normalized load conductance  $1/\omega CR_L$  for  $r_{w1}$  +  $n^2r_{w2}$  = 0.4  $\Omega$  and n = 6. The overall efficiency of the rectifier is

$$\eta = \eta_R \eta_T = \frac{P_O}{P_O + 2P_C + 2P_D + P_{Cu}}.$$

(24)

A plot of the rectifier efficiency  $\eta$  is depicted in Fig. 15.

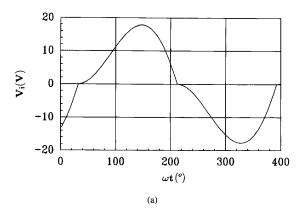

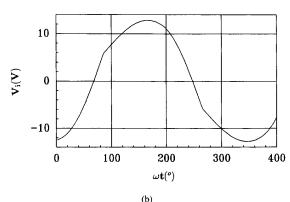

Fig. 16(a) and (b) show the waveforms of the voltage  $v_i$  across the primary winding of the transformers for D=0.5 and D=0.3, respectively. The waveform of the input voltage  $v_i$  has low harmonic content and is almost sinusoidal for  $D\leq 0.3$ .

The values of the rectifier parameters are summed up for design purposes in Table I.

## IV. DESIGN EXAMPLE

Design a Class E full-wave rectifier with the following specifications:  $V_O$  = 5 V and  $I_{O(max)}$  = 15 A. The minimum

Fig. 13. Voltage transfer function  $nM_R$  as functions of D and  $\omega CR_L$ . (a)  $nM_R$  versus D. (b)  $nM_R$  versus  $\omega CR_L$ .

load resistance is  $R_{Lmin}=V_O/I_{O(max)}=0.33~\Omega$  and the maximum load resistance is infinity. The maximum output power is  $P_{O(max)}=V_OI_{O(max)}=75$ W. The on-duty cycle of the diodes is assumed to be  $D_{max}=0.45$  at  $R_{Lmin}$  to get a high power-output capability and to avoid overlapping of the diode conduction. Using (7), the maximum value of the diode peak current is  $I_{DM}=1.654I_O=24.81$  A. From (10), the maximum value of the diode reverse voltage is  $V_{DRM}=3.345V_O=16.725$  V. Substitution of D=0.45 into (3) yields  $\omega CR_L=0.241$ . Assuming f=1 MHz, we have  $C_1=C_2=0.241/\omega R_L=114$  nF. The filter capacitor  $C_f$  is chosen to be 1 nF.

# V. EXPERIMENTAL VERIFICATION

To verify the results obtained from the theoretical analysis, a rectifier with the ratings given in Section IV was constructed and tested. The input current source was obtained by employing a Class E inverter coupled to the rectifier with two transformers built on EFD30 Siemens N49 ferrite cores. The primary winding of each transformer was obtained using 12 turns of litz wire with a total cross-sectional area of 0.47 mm<sup>2</sup>. The secondary winding of each device was built using 2 turns of a copper strip 15 mm wide and 0.12 mm high. Two Motorola Schottky MBR4035 diodes were used. The mean value of the diode current was overrated to reduce the diode forward voltage drop. The Schottky

(b) Fig. 14. Normalized rectifier transconductance  $nG_R$  as functions of D and  $\omega CR_L$ . (a)  $nG_R$  versus D. (b)  $nG_R$  versus  $\omega CR_L$ .

0

2

6

$\omega CR_L$

8

10

Fig. 15. Transformer efficiency  $\eta_T$ , rectifier efficiency  $\eta_R$ , and overall efficiency  $\eta$  as a function of  $1/\omega CR_L$ .

diode parasitic capacitances were included in the externally connected capacitors, each obtained by paralleling four 22 nF and two 10 nF Murata NPO capacitors. The NPO devices were used because their operating temperature is up to 95°C.

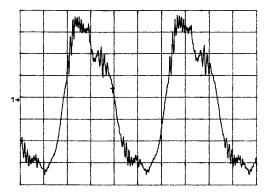

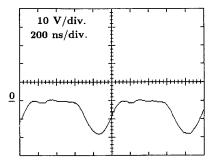

Fig. 17 displays an experimental waveform of the input voltage  $v_i$  at  $V_O=5$  V,  $I_O=8$  A, and f=0.922 MHz. Fig. 18 shows an experimental waveform of the diode voltage at  $V_O=5$  V,  $I_O=15$  A, and D=0.45. The peak diode voltage was  $V_{DM}=18$  V, while the predicted one was  $V_{DM}=16.7$

REATTI et al: CLASS E FULL-WAVE

Fig. 16. Waveform of the rectifier input voltage  $v_i$ . (a) At D=0.5. (b) At D=0.3.

TABLE I

PARAMETERS OF CLASS E FULL-WAVE LOW dv/dt RECTIFIER

| D    | φ (°)  | $\omega CR_L$ | $I_{DM}/I_O$ | $V_{DRM}/V_O$ | $R_i/n^2R_L$          | $\omega_r C R_i/n^2$ | $n^2C_i/C$ | $K_i/n$ | $c_{\rm p}$ |

|------|--------|---------------|--------------|---------------|-----------------------|----------------------|------------|---------|-------------|

| 0    | 180.00 | ∞             | ∞            | 2             | 0                     | 0                    | 0.251      | 0       | 0           |

| 0.05 | 160.32 | 62.669        | 19.84        | 2.022         | $2.01 \times 10^{-7}$ | $1.3 \times 10^{-5}$ | 0.256      | 0.022   | 0.025       |

| 0.1  | 143.85 | 14.982        | 9.702        | 2.079         | $2.5 \times 10^{-5}$  | 0.0004               | 0.264      | 0.086   | 0.049       |

| 0.15 | 128.14 | 6.199         | 6.241        | 2.164         | 0.001                 | 0.003                | 0.273      | 0.189   | 0.074       |

| 0.2  | 113.10 | 3.165         | 4.459        | 2.273         | 0.003                 | 0.001                | 0.286      | 0.324   | 0.099       |

| 0.25 | 98.63  | 1.793         | 3.356        | 2.406         | 0.015                 | 0.027                | 0.303      | 0.488   | 0.124       |

| 0.3  | 84.63  | 1.247         | 2.731        | 2.566         | 0.058                 | 0.059                | 0.327      | 0.672   | 0.144       |

| 0.35 | 71.04  | 0.729         | 2.201        | 2.754         | 0.163                 | 0.109                | 0.364      | 0.873   | 0.167       |

| 0.4  | 57.78  | 0.546         | 1.857        | 2.976         | 0.431                 | 0.178                | 0.420      | 1.084   | 0.183       |

| 0.45 | 44.80  | 0.241         | 1.654        | 3.241         | 1.032                 | 0.266                | 0.516      | 1.301   | 0.193       |

| 0.5  | 32.06  | 0.176         | 1.458        | 3.562         | 2.307                 | 0.362                | 0.703      | 1.519   | 0.196       |

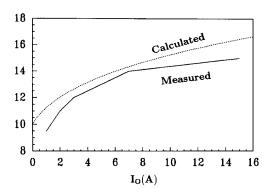

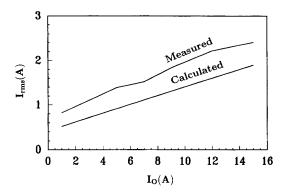

V, resulting in an error of 7%. Note that there were no oscillations because the parasitic capacitances of the diodes do not adversely affect the rectifier operation. A comparison of theoretical and experimental plots of the diode peak voltage is displayed in Fig. 19. Fig. 20 depicts plots of the calculated and measured rms input current.

# VI. CONCLUSIONS

A detailed analysis and experimental tests of a Class E full-wave rectifier have been presented. The results predicted theoretically are in good agreement with the experimental tests.

Fig. 17. Experimental waveform of the rectifier input voltage  $v_i$  at  $V_O=5$  V,  $I_O=8$  A, and f=0.922 MHz. Vertical: 10 V/div.; horizontal: 250 ns/div.

Fig. 18. Experimental waveform of the voltage across diode  $D_1$  at at  $V_O$  = 5 V,  $I_O$  = 15 A, f = 1.02 MHz, and D = 0.45.

The full-wave rectifier offers several advantages over the Class E half-wave rectifier. It has lower losses, lower THD, and theoretically zero-ripple output voltage. Common features of the Class E rectifiers are as follows. First, the diodes turn on with low dv/dt and turn off at zero current with low dv/dtand low di/dt. Second, current or voltage waveforms do not overlap at the diode transitions, thus significantly reducing the switching losses. Switching losses are also reduced because the reverse-recovery charge effect in pn junction diodes is reduced by the limited value of di/dt at the diode turn-off. Third, the noise level produced by the circuit is drastically reduced by the limited values of the derivatives of the diode current and voltage waveforms at the switching times. Finally, the detrimental effects of the Schottky diode parasitic capacitances are completely overcome by the parallel connection of external capacitors. Consequently, the Class E rectifiers are neither affected by the parasitic oscillations nor by switching losses which take place in a traditional rectifier.

Since the average current in each diode of the Class E full-wave circuit is one-half of that through the diode of the Class E half-wave rectifier, conduction losses in the former circuit are about one-half of those in the latter. Moreover, the Class E full-wave circuit has theoretically zero ac component of the output current. Actually, the ac component of the output current is about 10 times lower than in the half-wave circuit, and hence, losses in the filter capacitor are reduced 100 times lower. Also, diode conduction losses are lower than in the Class E half-wave rectifier. The efficiency is relatively high

Fig. 19. Measured and calculated maximum voltage across the diodes  $V_{DRM}$  as a function of the load current  $I_{O}$ .

Fig. 20. Measured and calculated rectifier input rms current as a function of the load current  $I_O$ .

and almost constant for an output current ranging from 10% to 100% of the full load. Also, the Class E full-wave circuit has a low THD. Because of these features, the rectifier is particularly suitable for high-frequency, high-power density applications requiring a low-output voltage and high-output current. To achieve the proper operation of the rectifier, the circuit must be symmetrical. Hence, the leakage inductances of the transformers must be controlled. This could represent a drawback in the practical realization of the rectifier circuit. Analysis and characterization of dc-dc converters including the Class E full-wave rectifier topologies are recommended for future research.

## APPENDIX: DERIVATION OF DESIGN EQUATIONS

Referring to Fig. 1, the primary winding of the transformers is driven by a sinusoidal current source given by (1). This current is reflected to the secondary winding of the full-wave transformers, which can be represented by two secondary magnetizing inductances and two current sources given by

$$i_1 = ni = nI_m sin\omega t \tag{25}$$

and

$$i_2 = -ni = -nI_m sin\omega t. (26)$$

The currents through the secondary magnetizing inductances are equal and expressed by

$$i_L = \frac{I_O}{2}. (27)$$

Using (25), (26), and (27), one obtains the current flowing through the parallel combination  $D_1$ – $C_1$

$$i_{C1} + i_{D1} = \frac{I_O}{2} + nI_m sin\omega t$$

(28)

and the current through the parallel combination  $D_2$ - $C_2$

$$i_{C2} + i_{D2} = \frac{I_O}{2} - nI_m sin\omega t.$$

(29)

# A. Mode I: $\phi < \omega t \le \phi + 2\pi D$

During this time interval, diode  $D_1$  is on and, therefore, the capacitor current  $i_{C1}$  is zero. Hence, the diode current is given by (28). Diode  $D_1$  turns off at the end of the first topological mode, when its current reaches zero, i.e.,  $i_{D1}(\phi+2\pi D)=0$ . Thus, from (28) one arrives at (4). Substitution of (4) into (28) yields the diode current  $i_{D1}$  given by (5). During this phase,  $D_2$  is off and the current through capacitor  $C_2$  is given by

$$i_{C2} = \frac{I_O}{2} - nI_m sin\omega t = \frac{I_O}{2} \left[ 1 + \frac{sin\omega t}{sin(\phi + 2\pi D)} \right]. \quad (30)$$

Though the first topological mode begins at  $\omega t = \phi$ , the voltage across the parallel combination  $D_2$ – $C_2$  is zero when  $\omega t = \phi + 2\pi D - \pi$ , i.e.,  $v_{C2}(\phi + 2\pi D - \pi) = 0$ . Thus, the voltage waveform across the combination  $C_2$ – $D_2$  is

$$= v_{D2} = \frac{1}{\omega C_2} \int_{\phi + 2\pi D - \pi}^{\omega t} i_{C2}(\omega t) d(\omega t)$$

$$= \frac{1}{\omega C_2} \int_{\phi + 2\pi D - \pi}^{\omega t} \frac{I_O}{2} \left[ 1 + \frac{\sin \omega t}{\sin(\phi + 2\pi D)} \right] d(\omega t)$$

$$= \frac{I_O}{2\omega C_2} \left[ (\omega t - \phi - 2\pi D + \pi) - \frac{\cos \omega t + \cos(\phi + 2\pi D)}{\sin(\phi + 2\pi D)} \right].$$

(21)

Substitution of  $I_O = V_O/R_L$  into (31) yields (9).

## B. Mode II: $\phi + 2\pi D < \omega t \le \phi + \pi$

This topological mode begins with the turn-off of  $D_1$ . The current flows through  $C_1$  and, according to (28) and (4), is given by

$$i_{C1} = \frac{I_O}{2} \left[ 1 - \frac{\sin \omega t}{\sin(\phi + 2\pi D)} \right]. \tag{32}$$

Since  $v_{C1}(\phi + 2\pi D) = 0$ , as shown in Fig. 3, the voltage across the parallel combination  $D_1 - C_1$  is expressed by

$$v_{C1} = v_{D1} = \frac{1}{\omega C_1} \int_{\phi+2\pi D}^{\omega t} i_{C1}(\omega t) d(\omega t)$$

$$= \frac{1}{\omega C_1} \int_{\phi+2\pi D}^{\omega t} \frac{I_O}{2} \left[ 1 - \frac{\sin \omega t}{\sin(\phi + 2\pi D)} \right] d(\omega t)$$

$$= \frac{I_O}{2\omega C_2} \left[ (\omega t - \phi - 2\pi D) - \frac{\cos \omega t - \cos(\phi + 2\pi D)}{\sin(\phi + 2\pi D)} \right]$$

(33)

which gives (8). In the lower section of the rectifier, diode  $D_2$  is still off and the current through  $C_2$  is given by (30).

C. Mode III:

$$\phi + \pi < \omega t \le \phi + \pi + 2\pi D$$

At the beginning of mode III, diode  $D_2$  is turned on. Hence, (30) represents the current  $i_{D2}$ , yielding (6). The current and voltage of  $C_1$  are still expressed by (32) and (33), respectively.

D. Mode IV:

$$\phi + \pi + 2\pi D < \omega t < \phi + 2\pi$$

During this time interval  $D_2$  is off and, therefore, the current through  $C_2$  is given by (30). Since  $v_{D2}(\phi+2\pi D+\pi)=0$ , the equation of the voltage waveform across the parallel combination  $D_2$ - $C_2$  is

$$v_{C2}$$

$$= v_{D2} = \frac{1}{\omega C_2} \int_{\phi+2\pi D+\pi}^{\omega t} i_{C2}(\omega t) d(\omega t)$$

$$= \frac{1}{\omega C_2} \int_{\phi+2\pi D+\pi}^{\omega t} \frac{I_O}{2} \left[ 1 + \frac{\sin \omega t}{\sin(\phi + 2\pi D)} \right] d(\omega t)$$

$$= \frac{I_O}{2\omega C_2} \left[ (\omega t - \phi - 2\pi D - \pi) - \frac{\cos \omega t + \cos(\phi + 2\pi D)}{\sin(\phi + 2\pi D)} \right]$$

(34)

which gives (9). The current and the voltage of  $D_1$  and  $C_1$  are still given by (33) and (32). Diode  $D_1$  turns on at zero voltage at the end of this time. Using (8) and the fact that  $v_{D1}(\phi+2\pi)=0$ , one arrives at (2).

The average reverse voltage across  $D_1$  is expressed by

$$-V_{O} = V_{D(av)} = \frac{1}{2\pi} \int_{\phi+2\pi D}^{\phi+2\pi} v_{D1}(\omega t) d(\omega t)$$

$$= \frac{V_{O}}{4\pi\omega C_{1}R_{L}} \left[ 2\pi^{2}(1-D)^{2} - 1 - 2\pi(1-D)\cot(2\pi D + \phi) + \frac{\sin\phi}{\sin(2\pi D + \phi)} \right].$$

(35)

Simplifying (35) gives (3).

As stated before, the rectifier input impedance is given by a series connection of a resistance  $R_i$  and a capacitance  $C_i$ . Their values can be evaluated at the operating frequency considering the input voltage of the rectifier given by different expressions, according to the topological configurations the circuit goes through during one switching period. Thus,

$$v_{i} = -nv_{D2}$$

$$= \frac{-nV_{O}}{2\omega CR_{L}} \left[ \omega t - \phi - 2\pi D + \pi - \frac{\cos \omega t + \cos(\phi + 2\pi D)}{\sin(\phi + 2\pi D)} \right],$$

for  $\phi < \omega t \le \phi + 2\pi D$  (36)

$$v_i = n(v_{D1} - v_{D2}) = \frac{nV_O}{2\omega CR_L} \left[ \pi + \frac{2cos\omega t}{sin(\phi + 2\pi D)} \right],$$

for  $\phi + 2\pi D < \omega t < \phi + \pi$  (37)

$$v_{i} = nv_{D1}$$

$$= \frac{nV_{O}}{2\omega CR_{L}} \left[ \omega t - \phi - 2\pi D + \frac{\cos \omega t - \cos(\phi + 2\pi D)}{\sin(\phi + 2\pi D)} \right],$$

for  $\phi + \pi < \omega t < \phi + \pi + 2\pi D$  (38)

83

$$v_{i} = n(v_{D1} - v_{D2}) = \frac{nV_{O}}{2\omega CR_{L}} \left[ \pi + \frac{2\cos\omega t}{2\sin(\phi + 2\pi D)} \right],$$

for  $\phi + \pi + 2\pi D < \omega t < \phi + 2\pi$ . (39)

Using (36)-(39) and Fourier expansion, the fundamental component of the input voltage becomes

$$v_{i1} = V_{Rim} sin\omega t + V_{Cim} sin\left(\omega t + \frac{\pi}{2}\right)$$

$$= V_{Rim} sin\omega t - V_{Cim} cos\omega t \tag{40}$$

and the amplitude  $V_{Rim}$  is expressed by

$$V_{Rim} = \frac{1}{\pi} \int_{\phi}^{\phi + 2\pi} v_i sin\omega t d(\omega t). \tag{41}$$

Substitution of (36)–(38) into (41) gives (12).

The amplitude  $V_{Cim}$  is given by

$$V_{Cim} = \frac{1}{\pi} \int_{\phi}^{\phi + 2\pi} v_i cos\omega t d(\omega t). \tag{42}$$

Using (36)-(38), one arrives at (14).

The conduction loss of each diode is given by

$$P_{D} = \frac{V_{F}I_{O}}{2} + r_{F}I_{Drms}^{2} \tag{43}$$

where  $I_{Drms}$  is the rms value of the diode current. From (5), the rms value of diode current is found as

$$I_{Drms} = \sqrt{\frac{1}{2\pi}} \int_{\phi}^{\phi+2\pi D} \left[ \frac{I_O}{2} (1 - \frac{\sin\omega t}{\sin(\phi + 2\pi D)}) \right]^2 d(\omega t)$$

$$= \frac{I_O}{2} \left[ D + \frac{2\pi D + \sin\phi\cos\phi}{4\pi \sin^2(\phi + 2\pi D)} + \frac{3}{4\pi \tan(\phi + 2\pi D)} - \frac{\cos\phi}{\pi \sin(\phi + 2\pi D)} \right]^{1/2}$$

(44)

Substitution of this into (43) gives

$$P_{D} = \frac{V_{F}I_{O}}{2} + \frac{r_{F}I_{O}^{2}}{4} \left[ D + \frac{D}{2sin^{2}(\phi + 2\pi D)} + \frac{3}{4\pi tan(\phi + 2\pi D)} - \frac{cos\phi}{\pi sin(\phi + 2\pi D)} + \frac{sin\phi cos\phi}{4\pi sin^{2}(\phi + 2\pi D)} \right]. \tag{45}$$

Using  $P_O = V_O I_O = R_L I_O^2$ , one obtains (19). The loss in each parallel capacitor is expressed by

$$P_C = r_{ESR} I_{Crms}^2. (46)$$

Using (5), the rms value of the current through the parallel capacitance  $C_1$  is given by

$$I_{Crms} = \sqrt{\frac{1}{2\pi} \int_{\phi+2\pi D}^{\phi+2\pi} \left[ \frac{I_O}{2} (1 - \frac{\sin\omega t}{\sin(\phi + 2\pi D)}) \right]^2 d(\omega t)}$$

$$= \frac{I_O}{2} \left[ 1 - D + \frac{1 - D}{2\sin^2(\phi + 2\pi D)} - \frac{3}{4\pi \tan(\phi + 2\pi D)} + \frac{\cos\phi}{\pi \sin(\phi + 2\pi D)} - \frac{\sin\phi\cos\phi}{4\pi \sin^2(\phi + 2\pi D)} \right]^{1/2}$$

$$(47)$$

Using (46) and substituting  $P_O = R_L I_O^2$ , one can find (20). The losses in the transformer windings are

$$P_{Cu} = (r_{w1} + n^2 r_{w2}) \frac{I_m^2}{2}. (48)$$

Substitution of (4) into this equation gives (22).

The efficiency of the transformers is expressed by

$$\eta_T = \frac{P_{To}}{P_{Ti}} \tag{49}$$

where  $P_{To}$  is the transformer output power and  $P_{Ti}$  is the transformer input power. Neglecting the core losses, we have

$$P_{Ti} = P_{To} + P_{Cu} = P_O + 2P_D + 2P_C + P_{Cu}.$$

(50)

Substitution of this into (49) yields (23).

## REFERENCES

- M. K. Kazimierczuk and J. Jóźwik, "Class E resonant rectifiers," in Proc. 31st Midwest Symp. Circuits and Systems, St. Louis, MO, Aug. 10–12, 1988, pp. 138–141.

—, "Class E zero-voltage-switching rectifier with a series capaci-

- [2] \_\_\_\_\_\_, "Class E zero-voltage-switching rectifier with a series capacitor," *IEEE Trans. Circuits Syst.*, vol. CAS-36, pp. 926–928, June 1989.

[3] M. K. Kazimierczuk, "Class E low dv<sub>D</sub>/dt rectifier," *Proc. Inst. Elec.*

- [3] M. K. Kazimierczuk, "Class E low dv<sub>D</sub>/dt rectifier," Proc. Inst. Elec. Eng., Pt. B, Electric Power Appl., vol. 136, pp. 257–262, Nov. 1989.

[4] M. K. Kazimierczuk and J. Jóźwik, "Class E zero-voltage-switching

- [4] M. K. Kazimierczuk and J. Jóźwik, "Class E zero-voltage-switching and zero-current-switching rectifiers," *IEEE Trans. Circuits Syst.*, vol. CAS-37, pp. 436-444, Mar. 1990.

- [5] M. K. Kazimierczuk, "Analysis of Class E zero-voltage-switching rectifier," *IEEE Trans. Circuits Syst.*, vol. CAS-37, pp. 747-755, June 1990.

- [6] M. K. Kazimierczuk and J. Jóźwik, "Analysis and design of Class E zero-current switching rectifier," *IEEE Trans. Circuits Syst.*, vol. CAS-37, pp. 1000-1009, Aug. 1990.

- [7] M. K. Kazimierczuk and K. Puczko, "Class E low dv/dt synchronous rectifier with controlled duty ratio and output voltage," *IEEE Trans. Circuits Syst.*, vol. CAS-38, pp. 1165-1172, Oct. 1991

- Circuits Syst., vol. CAS-38, pp. 1165-1172, Oct. 1991.

[8] M. K. Kazimierczuk and J. Jóźwik, "Resonant dc/dc converter with Class-E inverter and Class-E rectifier," *IEEE Trans. Ind. Electron.*, vol. IE-36, pp. 568-576, Nov. 1989.

- [9] N. O. Sokal and A. D. Sokal, "Class E A new Class of high-efficiency tuned single-ended switching power amplifiers," *IEEE J. Solid-State Circuits*, vol. SC-10, pp. 168-176, June 1975.

- [10] F. H. Raab, "Idealized operation of the Class E tuned power amplifier,"

IEEE Trans. Circuits Syst., vol. CAS-24, pp. 725-735, Dec. 1977.

- [11] F. H. Raab, "Effects of circuit variations on the Class E tuned power amplifier," *IEEE J. Solid-State Circuits*, vol. SC-13, pp. 239-247, Apr. 1078

- [12] M. K. Kazimierczuk, "Class E tuned power amplifier with shunt inductor," *IEEE J. Solid–State Circuits*, vol. SC-16, pp. 2-7, Feb. 1981.

- [13] R. E. Zulinski, "A high-efficiency self-regulated Class E power inverter/converter," *IEEE Trans. Ind. Electron.*, vol. IE-33, pp. 340-342, Aug. 1986.

- Aug. 1986.

[14] R. E. Zulinski and J. W. Steadman, "Class E power amplifiers and frequency multipliers with finite dc-feed inductance," *IEEE Trans. Circuits Syst.*, vol. CAS-34, pp. 1074–1087. Sept. 1987.

- [15] M. K. Kazimierczuk, "Exact analysis of Class E tuned power amplifier with only one inductor and one capacitor in load circuit," *IEEE J. Solid-State Circuits*, vol. SC-18, pp. 214–221, Apr. 1983.

- Solid-State Circuits, vol. SC-18, pp. 214-221, Apr. 1983.

[16] M. K. Kazimierczuk and K. Puczko, "Exact analysis of Class E tuned amplifier at any switch duty cycle," *IEEE Trans. Circuits Syst.*, vol. CAS-34, pp. 149-159. Feb. 1987.

- CAS-34, pp. 149-159, Feb. 1987.

[17] C. P. Avratoglou and N. C. Voulgaris, "A Class E tuned amplifier configuration with finite de-feed inductance and no capacitance in parallel," *IEEE Trans. Circuits Syst.*, vol. CAS-35, pp. 416-422, Apr. 1988.

- [18] M. K. Kazimierczuk and K. Puczko, "Class E tuned amplifier with an antiparallel or series diode at switch, with any loaded Q and switch duty cycle," *IEEE Trans. Circuits Syst.*, vol. CAS-36, pp. 1201–1209, Aug. 1989

- Aug. 1989.

[19] R. E. Zulinski and K. J. Grady, "Load-independent Class E power inverters Part I: Theoretical development," *IEEE Trans. Circuits Syst.*, vol. CAS-37, pp. 1010–1018, Aug. 1990.

- vol. CAS-37, pp. 1010-1018, Aug. 1990.

[20] M. K. Kazimierczuk and J. Jóźwik, "Class E<sup>2</sup> narrow-band resonant dc/dc converters," *IEEE Trans. Instrum. Meas.*, vol. IM-38, pp. 1064-1068, Dec. 1989.

- 21] \_\_\_\_\_\_, "Dc/dc converter with Class E zero-voltage-switching inverter and zero-current-switching rectifier," *IEEE Trans. Circuits Syst.*, vol. CAS-36, pp. 1485-1488, Nov. 1989.

- 22] J. Jóźwik and M. K. Kazimierczuk, "Analysis and design of Class E<sup>2</sup> dc/dc converter," *IEEE Trans. Ind. Electron.*, vol. IE–37, pp. 173–183, Apr. 1990.

**Alberto Reatti** received the M.S. degree in electronics engineering from the Department of Electronics Engineering, University of Florence, Italy, in 1986.

In the summer of 1992, he was a research associate with the Department of Electrical Engineering, Wright State University, Dayton, OH. He is currently working towards the Ph.D. degree at the Department of Electronics Engineering, University of Florence. His research interests are in high-frequency high-efficiency dc/dc power converters.

Marian K. Kazimierczuk received the M.S., Ph.D., and D. Sci. degrees in electronics engineering from the Department of Electronics, Technical University of Warsaw, Poland, in 1971, 1978, and 1984, respectively.

He was a teaching and research assistant from 1972 to 1978 and assistant professor from 1978 to 1984 with the Department of Electronics, Institute of Radio Electronics, Technical University of Warsaw. In 1984, he was a Project Engineer for Design Automation, Lexington, MA. In 1984–85 he was

a visiting professor with the Department of Electrical Engineering, Virginia Polytechnic Institute and State University, VA. Since 1985, he has been with the Department of Electrical Engineering, Wright State University, Dayton, OH, where he is currently an Associate Professor. His research interests are in high-frequency high-efficiency power tuned amplifiers, resonant dc/dc power converters, dc/ac inverters, high-frequency rectifiers, and lighting systems. He has published more than 100 technical papers, more than 50 of which have appeared in IEEE Transactions and Journals. He is an Associate Editor for the Journal of Circuits, Systems, and Computers.

In 1991, Dr. Kazimierczuk received the IEEE Harrell V. Noble Award for his contributions to the fields of aerospace, industrial, and power electronics. He is also a recipient of the 1991 Presidential Award for Faculty Excellence in Research and the 1993 Teaching Award from Wright State University.

Richard Redl received the diploma in telecommunications engineering and the Technical Doctor degree from the Technical University of Budapest,

degree from the Technical University of Budapest, Hungary.

At the Technical University of Budapest, from 1969 to 1984, he taught electronic circuits, conducted research in switching-mode power conversion and power amplification, and designed and managed design projects for numerous power supplies and power supply systems for industrial and space applications. From 1984 to 1989, he was a consultant in the United States. Since 1990, he has been the Director of ELFI SA, an electronics consulting company in Switzerland. He has written more than 60 technical papers and is co-author of a book on dynamic analysis of power converters.

power converters.