# Accurate Design of Output Filter for DC–DC PWM Buck Converter and Derived Topologies

Marian K. Kazimierczuk<sup>(D)</sup>, *Life Fellow, IEEE*, Gabriele Maria Lozito<sup>(D)</sup>, *Member, IEEE*, Fabio Corti<sup>(D)</sup>, *Member, IEEE*, and Alberto Reatti<sup>(D)</sup>, *Member, IEEE*

*Abstract*— This paper presents an analysis of an LCR secondorder low-pass filter capacitor to achieve a specified ripple output voltage in Buck, forward, Zeta, and Ćuk PWM DC-DC power converters for continuous-conduction mode (CCM). Current and voltage waveforms across output filter components are derived. Using the waveform of the ac component of the output voltage, an expression for the ripple voltage is developed in terms of the filter capacitance and equivalent series resistance. The results can be used for all PWM converters with the LCR output filter, such as Buck, forward, Zeta, and Ćuk PWM DC-DC converters. Theoretical results were in good agreement with simulation and experimental results.

*Index Terms*—Ripple voltage, equivalent series resistance (ESR), Buck converter, forward converter, Zeta converter, Ćuk converter, LCR second-order low-pass filter.

#### I. INTRODUCTION

**B** UCK, Forward, Zeta, and Ćuk PWM DC-DC power converters have the same topology of an LCR second-order low-pass output filter. The filter capacitor can be modeled as a series combination of a capacitance and an equivalent series resistance (ESR) for frequencies much lower than the selfresonant frequency. The ac component of the converter output voltage is the sum of the ac component of the voltage across the capacitance and the voltage across the equivalent series resistance. The peak-to-peak voltage across the capacitance and the peak-to-peak voltage across the equivalent resistance are shifted in phase. Therefore, the ripple output voltage is not always equal to the sum of these peak-to-peak voltages. In [1] and [2] the case when the ripple voltage is solely equal to the ripple voltage across the equivalent series resistance was considered. The objective of this paper is to extend the previous analysis for the case when the ripple voltage is determined by the contributions of voltages across both the filter capacitance and the equivalent series resistance in

Manuscript received 13 September 2022; revised 7 December 2022; accepted 16 January 2023. This article was recommended by Associate Editor F. M. Neri. (*Corresponding author: Fabio Corti.*)

Marian K. Kazimierczuk is with the Department of Electrical Engineering, Wright State University, Dayton, OH 45435 USA (e-mail: marian. kazimierczuk@wright.edu).

Gabriele Maria Lozito and Alberto Reatti are with the DINFO Department, University of Florence, 50139 Florence, Italy (e-mail: gabrielemaria.lozito@unifi.it; alberto.reatti@unifi.it).

Fabio Corti is with the Engineering Department, University of Perugia, 06125 Perugia, Italy (e-mail: fabio.corti@unipg.it).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCSI.2023.3238209.

Digital Object Identifier 10.1109/TCSI.2023.3238209

converters with LCR output filter for CCM. Buck, forward, Zeta, and Ćuk converters contain an LCR second-order output filter [2], [3]. The issue of filter design is widely discussed in the literature. A filter for dc-ac converters connected to the grid is an item much more investigated than the filter design for power converters [4], [5], [6]. The output filters of power converters are considered for their effect on the circuit dynamic in [7], which is mainly devoted to an input filter for dc-dc power converters based on active components. An approach based on a small-signal model is given in [8]. Papers [7] and [8] do not face the problem of the filter component value selection. The LC filter of a sigma-delta Boost Converter is studied in [9] to investigate the worst-case design LC combination and look at tolerance and/or variable design targets in power supplies for portable electronics, where low output voltage ripples are needed. Therefore, this paper does not consider an LC filter. An LC filter is investigated in [10], but this is an LC filter used as a low-pass filter a low-cost class-D audio amplifier. The occurrence of symmetry-breaking bifurcation in the series-parallel load-resonant dc-dc converter with LC output filter is investigated in [11]. Filters considered in [10] and [11] are operated with different waveforms than the LC filter investigated in this paper and, therefore, they require different design procedures than that proposed in this paper. The advantages introduced in a Zeta converter by a second-order LC filter are discussed in [12]. A third-order passive switched-capacitor low-pass filter is presented together with experimental results in [13], and the potentials provided by a push-pull forward three-level converter, allowing the output filter inductor ripple current to be reduced are studied in [14]. Despite the accurate analyses provided, [12], [13], [14] do not involve the design of the converter LC output filter. Some design procedures are available in [15] and [16]. An algebraic unified design method for the selection of capacitors in dc-dc switching converters for a PWM dc-dc SEPIC converter is given in [15]. Here, the capacitance C and its equivalent series resistance (ESR) of capacitors are included in a model and commercially available values of the capacitors are considered. The design procedure is based on piecewisedefined algebraic function, which determines and expresses the boundary of the capacitor acceptability region in a C-ESR plane. The Pareto algorithm for a design procedure provided in [16] starts with the assumption of random values for the filter components, and the algorithm changes these values in the attempt to achieve the minimum power losses. According to

1

1549-8328 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information. the author conclusions, the design procedure does not lead to a univocal sizing of the filter components, but rather, to different sets of values resulting in an "optimum" design.

Both the procedures given in [15] and [16] require cumbersome mathematical algorithms and have low practical applicability.

The property of a real capacitor can be described by its time constant  $\tau = Cr_C$ . Capacitor time constants are in the range of 80-100  $\mu$ s for electrolytic capacitors [17] and 60-80 ns for ceramic capacitors [18]. In [19] and [20], these time constants are utilized to choose the capacitance value as follows. The allowed capacitor ESR is derived according to  $r_{Cmax} = V_{rCpp} / \Delta i_L$ , where  $V_{rCpp}$  is the voltage ripple across the resistance  $r_C$  and  $\Delta i_L$  is the current ripple of the inductor, which is equal to the current ripple of resistor  $r_C$ . Then, the capacitance is determined by using  $C = \tau / r_{Cmax}$ . The limitation of this method is that  $V_{rCpp}$  is assumed a priorly, while the design specifications refer to the overall voltage ripple  $V_r$  of the output voltage  $v_o$ , which is given by both the ripple of the voltage across the ideal capacitor  $(v_C)$ , and that across its ESR  $(v_{rC})$ .

The purposes of this paper are to derive analytical equations of the two ripple components and use their accuracy to properly select the filter capacitor. Voltage and current waveforms of output filter components are derived and used to determine the analytical expressions for the ripple voltage components. A guideline for the selection of filter capacitor is given. The component values should be accurately predicted for high-frequency high-power density DC-DC converters, manufactured with surface-mount technology (SMT) and RF layout techniques.

In addition, the lower the filter capacitance, the faster is the transient response of the converter to changes in the duty cycle, input voltage, and load current.

Surface-mount assembly of converter components eliminates capacitor leads and reduces the ESR and the equivalent series inductance (ESL). A low filter capacitance with low ESL allows for achieving a high self-resonant frequency. These properties are required for filter capacitors of high-frequency SMPS operated above 1 MHz. This is because the capacitor self-resonant frequency is in the MHz range for electrolytic devices [17] and in the tens of MHz range for ceramic components [18].

#### II. VOLTAGE AND CURRENT WAVEFORMS

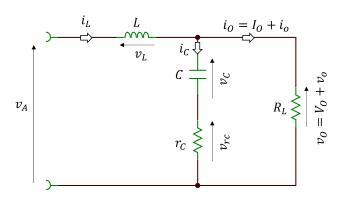

An equivalent circuit of the low-pass output filter used in the Buck, Forward, Zeta, and Ćuk converters is shown in Fig. 1. The filter capacitor is modeled as a series combination of capacitance *C* and series equivalent resistance  $r_C$ . Surfacemounted capacitors are leadless and have a very low equivalent series inductance (ESL), and therefore it is neglected in this work. The voltage drop across capacitance *C* consists of the dc component  $V_{C(DC)} = V_O$  and the ac component  $v_C$ . The output voltage  $v_O$  consists of the dc component  $V_O$  and the ac component  $v_o$ , where  $v_o$  is the sum of the ac component of the voltage  $v_c$  across the capacitance *C* and the voltage  $v_{rC}$  across the equivalent series resistance  $r_C$ . Current  $i_L$  is the overall

Fig. 1. Equivalent circuit of a second-order low-pass output filter in Buck, Forward, Zeta, and Ćuk DC-DC power converters.

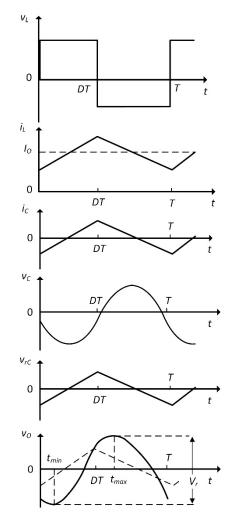

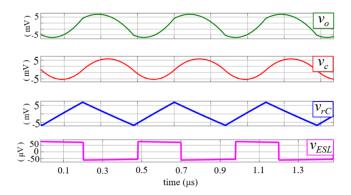

Fig. 2. Waveforms of the output network in the PWM Buck power converter for CCM.

current through inductor L, where  $i_L = I_L + \iota_l$ , as shown in Fig. 2,  $I_O = Vo / R_L = I_L$  is the current dc component, which flows through the load resistance  $R_L$ . The inductor ac component is divided between the capacitor C and the load resistor  $R_L$ . In real circuit, the peak-to peak currents through capacitor and inductor  $\Delta i_L$  are approximately equal.

The proposed analysis assumes that the self-resonant frequency of the filter capacitor is much higher than the converter switching frequency  $f_s$ . Fig. 2 shows current and voltage waveforms in the singlephase converter output circuit for CCM for steady-state operation. The input voltage of the converter output network  $v_A$ is a rectangular wave with a duty cycle D and shifted up by the dc component of the output voltage  $V_O$ . The voltage  $v_L = v_A - V_O$  across inductor L is a rectangular wave. Thus, the waveform of the inductor current  $i_L$  is triangular.

The filter capacitor is designed in such a way that its impedance magnitude is much lower than the load resistance  $R_L$  for  $f > f_s$ . Therefore, the current through the capacitor branch that consists of a series combination of the capacitance and its ESR is approximately equal to the ac component of the inductor current, i.e.,  $i_C \approx i_L$  -  $I_O$ . Hence, both the current  $i_C$  through capacitance C and the voltage drop across the resistance  $r_C$  are triangular. The ac component of the voltage  $v_c$  across the capacitance C consists of two parabolas, one with wings up and one with wings down. The ac component of the output voltage  $v_0$  is the sum of the voltages  $v_{rC}$  and  $v_C$ . The maximum peak-to-peak value of the output voltage across  $R_L$  is the ripple voltage  $V_r$ . The peak-to-peak voltages across resistance  $r_C$  and the peak-to-peak voltage across capacitance C are shifted in phase by  $90^{\circ}$ . Therefore, the ripple voltage  $V_{\rm r}$  is not always equal to the sum of the ripple voltage across the resistance and across the capacitance. This paper considers the case when both voltages  $v_{rC}$  and  $v_{C}$  contribute to ripple voltage  $V_r$ . The case when the ripple voltage is solely determined by the voltage across  $r_C$  was studied in [1].

Under the assumption that ESR is low and therefore, the time constant  $\tau = Cr_C$  is short, the output voltage exhibits both a minimum value and a maximum value inside a switching period. Note that in practice, a filter capacitor can be assembled by using two or more capacitors connected in parallel and this results in a lower ESR.

For the time interval  $0 < t \le DT$ , when the switch is ON and the diode is OFF, the current through the capacitor is given by

$$i_C \approx i_L - I_O = \frac{\Delta i_L}{DT} t - \frac{\Delta i_L}{2},\tag{1}$$

where  $\Delta i_L$  is the peak-to-peak inductor ripple current. The ac component of the voltage across resistor  $r_C$  is

$$v_{rc} = r_C i_C = r_C \Delta i_L \left(\frac{t}{DT} - \frac{1}{2}\right). \tag{2}$$

The ac component of the voltage across the filter capacitance is

$$v_c = \frac{1}{C} \int_0^t i_C dt + v_c (0) = \frac{\Delta i_L}{2C} \left( \frac{t^2}{DT} - t \right) + v_c (0).$$

(3)

The ac component of the output voltage is the sum of voltage across resistance  $r_C$  and capacitance C

$$v_o = v_{rc} + v_c$$

=  $\Delta i_L \left[ \frac{t^2}{2CDT} + \left( \frac{r_C}{DT} - \frac{1}{2C} \right) t - \frac{r_C}{2} \right] + v_c(0).$  (4)

For time interval  $DT < t \le T$ , the current through capacitor *C* is

$$i_C = -\frac{\Delta i_L}{(1-D)T}(t-DT) + \frac{\Delta i_L}{2},$$

(5)

yielding the voltage across  $r_C$

$$v_{rc} = r_C i_C = r_C \Delta i_L \left[ -\frac{t - DT}{(1 - D)T} + \frac{1}{2} \right]$$

(6)

and the voltage across the capacitor C

$$v_{c} = \frac{\Delta i_{L}}{2C} \left[ -\frac{t^{2} - 2DTt + (DT)^{2}}{(1 - D)T} + t - DT \right] + v_{c} (DT).$$

(7)

The ac component of the output voltage is

$$v_{o} = r_{C} \Delta i_{L} \left[ -\frac{t - DT}{(1 - D)T} + \frac{1}{2} \right] + \frac{\Delta i_{L}}{2C} \left[ -\frac{t^{2} - 2DTt + (DT)^{2}}{(1 - D)T} + t - DT \right] + v_{c} (DT).$$

(8)

For steady-state operation, the average value of the ac component of the capacitor voltage  $v_c$  is zero

$$\frac{1}{T} \int_0^T v_c dt = 0 \tag{9}$$

Producing

$$v_c(0) = v_c(DT) = \frac{\Delta i_L(2D - 1)}{12 f_s C}.$$

(10)

For  $0 < t \leq DT$ ,

$$v_o = v_{rc} + v_c$$

=  $\frac{\Delta i_L}{C} \left[ \frac{t^2}{2DT} + \left( \frac{r_C C}{DT} - \frac{1}{2} \right) t - \frac{r_C C}{2} + \frac{(2D-1)}{12f_s} \right].$  (11)

The derivative of the voltage vo with respect to time is

$$\frac{dv_o}{dt} = \Delta i_L \left( \frac{t}{CDT} + \frac{r_C}{DT} - \frac{1}{2C} \right) = 0$$

(12)

and minimum value of  $v_o$  occurs at time

$$t_{min} = \frac{DT}{2} - r_c C, \qquad (13)$$

which gives the minimum value of the ac component of the output voltage

$$V_{omin} = v_o (t_{min}) = -\frac{\Delta i_L}{C} \left[ \frac{D^2 T^2 + 4 (r_C C)^2}{8DT} \right] + v_c (0) = \frac{\Delta i_L}{C} \left[ \frac{2 - D}{24 f_s} + \frac{f_s (r_C C)^2}{2D} \right]$$

(14)

For  $DT < t \leq T$ ,

$$v_{o} = \frac{\Delta i_{L}}{C} \left\{ r_{C} C \left[ -\frac{t - DT}{(1 - D)T} + \frac{1}{2} \right] + \frac{1}{2} \left[ -\frac{t^{2} - 2DTt + (DT)^{2}}{(1 - D)T} + t - DT \right] \right\} + v_{c} (DT).$$

(15)

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS

The derivative of the voltage  $v_o$  with respect to time is

$$\frac{dv_o}{dt} = -\frac{r_C \Delta i_L}{(1-D) T} + \frac{\Delta i_L}{C} \left[ -\frac{t-DT}{(1-D) T} + \frac{1}{2} \right] \quad (16)$$

the maximum value of  $v_o$  occurs at time

$$t_{max} = \frac{(1-D)T}{2} - r_c C.$$

(17)

Then, the maximum value of the ac component of the output voltage is

$$V_{omax} = v_o(t_{max}) = \frac{\Delta i_L}{C} \left[ \frac{1 - D}{8f_s} + \frac{f_s(r_C C)^2}{2(1 - D)} \right].$$

(18)

### III. RIPPLE VOLTAGE

The ripple voltage ripple is obtained using (14) and (18)

$$V_{r} = V_{omax} - V_{omin} = \frac{\Delta i_{L}}{8f_{s}C} + \frac{\Delta i_{L}f_{s}r_{C}^{2}C}{2D(1-D)}i_{L}r_{C}\frac{f_{s}r_{C}C}{2D(1-D)} = V_{Cpp} + \frac{1}{2D(1-D)}\frac{\tau_{C}}{T_{s}}V_{rCpp} = V_{Cpp} + \Delta V_{pp},$$

(19)

where the peak-to-peak voltage across capacitance C is

$$V_{Cpp} = \frac{\Delta \iota_L}{8f_s C} \tag{20}$$

the peak-to-peak voltage across the resistance  $r_C$  is

$$V_{rCpp} = \Delta i_L r_C \tag{21}$$

and

$$\Delta V_{pp} = K_{VrCpp} V_{rCpp} = \frac{\tau_C}{T_S} \frac{1}{2D (1-D)} V_{rCpp}.$$

(22)

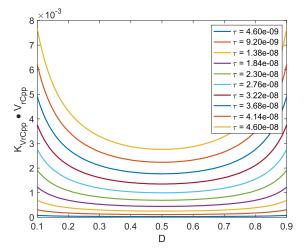

The expression given in (22) affects the overall ripple, also because of a multiplying factor, which depends on the duty cycle *D*. The plot of  $\Delta V_{pp}$  is given in Fig. 3 and shows that at *D* lower than 0.2 and higher than 0.8, the factor is much higher than its minimum value occurring at *D* =0.5. That is, even a low value of the ripple across the resistance can highly affect the overall ripple when the duty cycle is very low or close to unity.

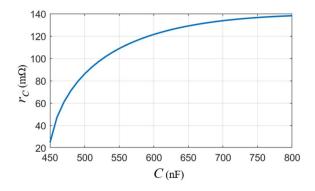

Fig. 4 shows capacitance *C* as a function of equivalent series resistance  $r_C$  for  $V_r = 21$  mV, D = 0.4444,  $\Delta i_L = 0.15$  A, and  $f_s = 2$  MHz. As the equivalent series resistance  $r_C$  decreases, capacitance *C* also decreases for a specified ripple voltage  $V_r$ .

For  $r_C = 0$ , the ripple voltage obtained from (19) is solely determined by the voltage drop across capacitance *C* as given by (20). The ESR of the filter capacitor is

$$r_{C} = \sqrt{\frac{2D(1-D)V_{r}}{f_{s}C\Delta i_{L}} - \frac{D(1-D)}{4f_{s}^{2}C^{2}}}$$

(23)

where (23) is obtained from (19) by manipulation. Fig. 4 shows equivalent series resistance  $r_C$  as a function of capacitance *C*, at fixed ripple voltage  $V_r = 21$  mV.

The maximum allowed equivalent series resistance is

$$r_{Cmax} = \frac{V_r}{\Delta i_{Lmax}}.$$

(24)

Fig. 3. Resistance voltage ripple multiplier as a function of duty cycle D.

Fig. 4. Equivalent series resistance  $r_C$  as a function of capacitance C for  $V_r = 21$  mV, D = 0.4444,  $\Delta i_L = 0.15$  A, and  $f_s = 2$  MHz.

For  $r_C = r_{Cmax}$ , the ripple voltage  $V_r$  is solely determined by the voltage drop across equivalent series resistance  $r_C$  [1], [2] if the capacitance C is larger than the critical capacitance  $C_B$

$$C > C_B = \frac{\max\{D_{max}, 1 - D_{min}\}}{2f_s r_C}.$$

(25)

For example, for  $V_r = 21$  mV and  $\Delta i_L = 0.15$  A, the maximum equivalent series resistance is  $r_{Cmax} = V_r / \Delta i_L = 0.021/0.15 = 0.14 \ \Omega$  and the critical capacitance  $C_B = 0.444/(2 \cdot 2 \cdot 10^6 \cdot 0.14) = 793.6$  nF. The critical capacitance calculated from (20) at  $r_C = 0.14 \ \Omega$  is  $C_B = 796.4$  nF. Pick a standard capacitance  $C = 1 \ \mu$ F. The resistance  $r_C$  calculated from (23) at  $C = 1 \ \mu$ F is  $r_C = 0.138 \ \Omega$ .

The proposed procedure to select the appropriate capacitance and its ESR for any given specification is as follows:

- 1) Assign the voltage ripple among C and its ESR.

- 2) Calculate C from (20) by using the assigned ripple voltage across the capacitance.

- 3) Select the standard practical capacitance value, higher and closest to the value determined in b).

- 4) Determine the maximum allowed ESR from (23).

- 5) Verify the voltage ripple by using (19).

- 6) Pick the capacitor with a practical value of  $r_C$  from data sheets.

7) Verify the voltage ripple according to practical values of C and  $r_C$ .

For example, consider a power converter operated at a switching frequency  $f_s = 2$  MHz with a maximum inductor current ripple  $\Delta i_L = 0.15$  A, a duty cycle D = 0.444, and a maximum allowed voltage ripple  $V_r = 21$  mV. If we assume that the overall ripple is divided as 80% across the filter capacitance and 20% across its ESR, the allowed voltage ripple across C and its ESR are 16.8 mV and 4.2 mV, respectively. Manipulation of (20) gives

$$C = \frac{\Delta i_L}{8f_s V_{Cpp}} = \frac{0.15}{8 \cdot 2 \cdot 10^6 \cdot 0.0168} = 558$$

nF. (26)

By substituting this value in (23) or in plot shown in Fig. 4, the maximum allowed capacitor ESR is derived as  $r_C = 111.87 \text{ m}\Omega$ . Substitution of these values into (19) gives the theoretical ripple voltage as

$$V_r = V_{Cpp} + \Delta V_{pp} = 16.74 + 4.26 = 21 \text{mV},$$

(27)

which confirms the validity of the theoretical derivations.

The closest commercial value of capacitor available in Kyocera AVX catalog [18] is 560 nF and this is the practical capacitance value to be considered for this example. The magnitude of the impedance for a surface mount capacitor has been derived by [18] LOCALREF the overall device impedance is given as  $|Z| = 0.1 \Omega$  at f = 2 MHz and, therefore, the 560 nF capacitor ESR is calculated as  $r_C = 94.05 \text{ m}\Omega$ . By using (19), the ripple voltage calculated for practical values is

$$V_r = V_{Cpp} + \Delta V_{pp} = 16.74 + 3.01 = 19.75 \text{mV}.$$

(28)

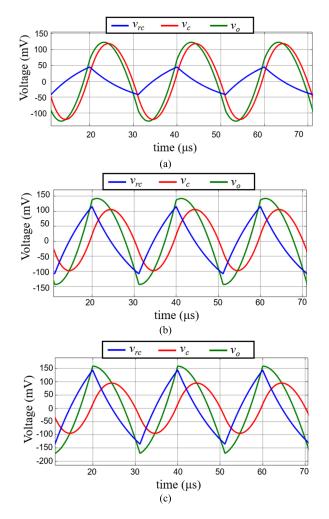

and  $V_{rCpp} = 0.15.94 \text{ m}\Omega = 14.1 \text{ mV}$ . The output voltage ripple ac components for this example are shown in Fig. 6(a). This value is lower than that given by (27) because the practical capacitance is slightly higher than the theoretical one and the practical ESR is lower than the theoretical one. This example shows a case where  $V_{Cpp}$  is dominant, but  $V_{rC}$  is still important.

Catalog [18] shows that the self-resonant frequency of the selected capacitor is 20 MHz, which makes the voltages across the equivalent series inductance (ESL) negligible at 2 MHz. This assumption has been confirmed by the simulation results shown in Fig. 5, where an ESL has been placed in series with C and  $r_C$ , to consider the self-resonant frequency. As shown, the voltage across the ESL  $v_{ESL}$  is of the order of tens of  $\mu$ V, while the voltages amplitudes across the capacitance  $v_C$ and across its equivalent series resistance ESR  $v_{rC}$  are two orders of magnitude higher. Therefore, the contribution of the voltage across the ESL  $v_{ESL}$  to the output voltage ripple  $V_r$  is negligible. At the self-resonant frequency as high as 20 MHz and capacitance C = 560 nF, the ESL is as low as  $L_C =$ 132 pH, which means that an inductive reactance as low as  $X_L = 1.42 \text{ m}\Omega$  at the switching frequency  $f_s = 2 \text{ MHz}$  versus the capacitive reactance  $X_C = 142.17 \text{ m}\Omega$  and an ESR  $r_C =$ 94.05 mΩ.

One more example, where  $V_{rCpp}$  is negligible, is given below. Assume that the overall ripple is divided as 98% on the filter capacitor and 2% on its ESR. In such a case, the

Fig. 5. Voltage and current waveforms in the LCR output filter showing a negligible contribution of the voltage across the Equivalent Series Inductance (ESL) to the output voltage ripple.

allowed voltage ripple on C and its ESR are 20.6 mV and 0.42 mV, respectively. Manipulation of (21) gives

$$C = \frac{\Delta i_L}{8f_s V_{Cpp}} = \frac{0.15}{8 \cdot 2 \cdot 10^6 \cdot 0.00206} = 455 \text{nF.}$$

(29)

The closest commercial value of capacitance available on Kyocera AVX catalogue [21] is 0.47  $\mu$ F and this is the practical capacitance value considered for this example. Moreover, from the Kyocera catalogue such a capacitance has  $r_C = 50.85 \text{ m}\Omega$ . By substituting the practical values in (19), the ripple voltage is calculated as

$$V_r = V_{Cpp} + \Delta V_{pp} = 19.94 + 0.74 = 20.68 \text{mV}.$$

(30)

and  $V_{rCpp} = 0.15.50.85 \text{ m}\Omega = 7.62 \text{ mV}$ . The waveforms of the ripple ac components are shown in Fig. 6(b).

Returning to theoretical values, substitution of C = 455 nF into (23) gives a maximum allowed ESR of  $r_C = 60.71$  m $\Omega$ , and substitution of these values into (19) allows for the theoretical ripple to be calculated as

$$V_r = V_{Cpp} + \Delta V_{pp} = 19.94 + 1.06 = 21 \text{mV}$$

(31)

which confirms the derivation introduced in this paper.

#### **IV. SIMULATION RESULTS**

The circuits resulting from the examples shown above were simulated and the plots of ripple voltages are shown in Fig. 6 (a) and (b) for the first example (C = 560 nF and  $r_C = 94.05 \text{ m}\Omega$ ) and the second one (C = 470 nF and  $r_C = 50.85 \text{ m}\Omega$ ), respectively. The plotted waveforms reflect the design calculations and confirm the accuracy of the proposed design procedure.

One more example referring to an LCR filter was considered to show that the proposed method is general and to investigate the effects of the capacitor ESR for a given capacitance value. In Fig. 7, the simulated waveforms are shown for the following the component values and operating parameters:  $\Delta i_L = 0.15$  A, obtained with a power inductor  $L = 220 \ \mu$ H and  $f_s = 50$  kHz,  $R_L = 4.98 \ \Omega$ ,  $V_I = 9$  V,  $V_O = 3.96$  V, D =0.44. The maximum allowed voltage ripple is  $V_r = 300$  mV.

Fig. 7 shows the simulated waveforms of the voltages across the filter capacitance  $v_C$ , the equivalent series resistance  $v_{rc}$ ,

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS

Fig. 6. Waveforms of  $v_C$ , ac components of voltage across filter capacitance C, voltage  $v_{rc}$  across equivalent series resistance  $r_C$ , and voltage  $v_o$ , ac component of voltage across load resistance  $R_L$  at D = 0.44,  $\Delta i_L = 0.15$  A, and  $f_s = 2$  MHz. (a) C = 560 nF and  $r_C = 0.94 \Omega$ . (b) C = 470 nF and  $r_C = 0.51 \Omega$ .

TABLE I BUCK CONVERTER THEORETICAL VOLTAGE RIPPLES

| $r_C(\Omega)$ | $V_r (\mathrm{mV})$ | $V_{Cpp}$ (mV) | $V_{rC}$ (mV) |

|---------------|---------------------|----------------|---------------|

| 0.5           | 238                 | 230            | 87.5          |

| 1.5           | 261                 | 197            | 224           |

| 2             | 298                 | 184            | 280           |

and the output voltage  $v_o$ . The waveforms are shown for three cases. In Fig. 7(a), the peak-to-peak voltage across the capacitance is higher than that across the resistance. In Fig. 7(b), the two voltages have comparable peak-to-peak values. In Fig. 7(c), the ripple voltage is equal to the peakto-peak voltage across the resistance  $r_C$  [1]. The component values for the simulation shown in Fig. 7(c) were calculated according to the procedure introduced in the previous section. The calculated peak-to-peak values of the voltages for the three cases agreed very well with the simulation results.

According to the provided design procedure, an overall ripple  $V_r = 300$ mV is obtained by using a  $C = 1.9 \ \mu$ F capacitance. Several ESRs are considered here according to the values shown in Table I to show the effects on the output voltage of ESRs. Table I also shows the different values of the voltages derived according to the theoretical analysis. Table II shows the values obtained from the simulations and Table III shows the errors among the theoretical and simulated voltage ripples.

#### V. EXPERIMENTAL RESULTS

A Buck converter with the same voltages and current specifications, as well the same component values as the simulated

Fig. 7. Waveforms of voltage  $v_C$  across filter capacitance C, voltage  $v_{rC}$  across equivalent series resistance  $r_C$ , and ac component of voltage  $v_o$  across load resistance  $R_L$ ,  $V_{rmax} = 200$  mV, D=0.44,  $\Delta i_L = 0.15$  A, and  $f_s = 50$  kHz, C=1.9  $\mu$ F (a)  $r_C = 0.5 \Omega$  when  $V_{Cpp} > V_{rCpp}$ . (b)  $r_C = 1.5 \Omega$  when  $V_{Cpp} \approx V_{rCpp}$ . (c)  $r_C = 2\Omega$  when  $V_{Cpp} < V_{rCpp}$ .

TABLE II SIMULATED BUCK CONVERTER VOLTAGE RIPPLES

| $r_{C}(\Omega)$ | $V_r (\mathrm{mV})$ | $V_{Cpp}$ (mV) | $V_{rC}$ (mV) |

|-----------------|---------------------|----------------|---------------|

| 0.5             | 247                 | 235            | 87.2          |

| 1.5             | 279                 | 204            | 225           |

| 2               | 300                 | 189            | 281           |

TABLE III Errors Among Theoretical and Simulated Voltage Ripples

| $r_{C}\left(\Omega ight)$ | $V_{rerr}$ (%) | V <sub>Cpperr</sub> (%) | VrCerr (%) |

|---------------------------|----------------|-------------------------|------------|

| 0.5                       | 3.64           | 2.12                    | 0.34       |

| 1.5                       | 6.45           | 3.43                    | 0.44       |

| 2                         | 0.66           | 2.64                    | 0.35       |

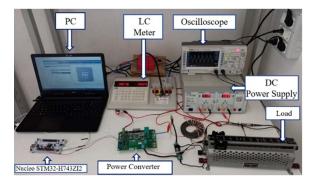

circuit, has been designed and assembled to run experimental tests and validate the theoretical predictions. The utilized experimental set-up is shown in Fig. 8. The Buck converter

Fig. 8. Experimental Setup.

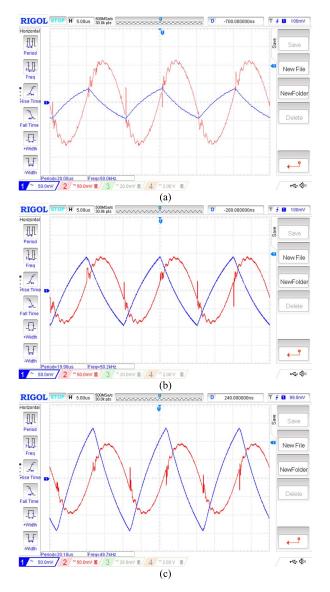

Fig. 9. Experimentally measured waveforms of voltage  $v_C$  across filter capacitance C (blue traces), and voltage  $v_{rC}$  across equivalent series resistance  $r_C$  (Yellow traces) for  $V_{rmax} = 200$  mV, D = 0.4444,  $\Delta i_L = 0.15$  A, and  $f_s = 50$  kHz,  $C = 1.9 \ \mu$ F (a)  $r_C = 0.5 \ \Omega$  when  $V_{Cpp} > V_{rCpp}$ . (b)  $r_C = 1.5 \ \Omega$  when  $V_{Cpp} \approx V_{rCpp}$ . (c)  $r_C = 2 \ \Omega$  when  $V_{Cpp} < V_{rCpp}$ .

has been assembled on a GS665EVBMB GaN Evaluation Board and the voltage waveforms were acquired by using a Rigol DS1054Z digital oscilloscope and Rigol, Model PVP

TABLE IV Measured Buck Converter Voltage Ripples

| $r_{C}\left( \Omega ight)$ | $V_C (\mathrm{mV})$ | $V_{rC}$ (mV) |

|----------------------------|---------------------|---------------|

| 0.5                        | 236                 | 85            |

| 1.5                        | 197                 | 196           |

| 2                          | 192                 | 285           |

| TABLE V                                                                |

|------------------------------------------------------------------------|

| $\operatorname{Errors}$ Among Theoretical and Measured Voltage Ripples |

| $r_C(\Omega)$ | $V_{Cpperr}$ (%) | $V_{rCerr}$ (%) |

|---------------|------------------|-----------------|

| 0.5           | 0.42             | 2.94            |

| 1.5           | 0.461            | 1.29            |

| 2             | 1.56             | 1.40            |

2350 voltage probes. The board contains two GaN E-HEMT GS66508B power MOSFETs with a 650 V breakdown voltage and 50 m $\Omega$  channel on-resistance. The inductance was constructed by winding on a 5978015901 MnZn 10 turns of Litz wire made up of 1800 strands of AWG36 wires. The inductance measured by using a Thurlby Thandar Precision LCR Bridge LCR 400 shown in Fig. 8 is  $L = 219.7 \ \mu \text{H}$ and its ESR is  $r_L = 26 \text{ m}\Omega$  measured at 50 kHz. The PWM signal was provided to the evaluation board using the Nucleo STM32-H743ZI2 control board. The experimental tests were focused on the determination of the voltage ripple components across the filter capacitance and the resistance connected in series with the capacitor. The 1.9  $\mu$ F capacitance was obtained by connecting in parallel six SNFP X0 2330 7D 4A KS00 WIMA capacitors with nominal values  $C_{nom} = 33$  nF. The resistance utilized to run the measurements was obtained by external resistors connected to achieve the desired values: 0.5  $\Omega$ , 1.5  $\Omega$ , and 2  $\Omega$ . These values were much higher than that of the overall capacitor ESR, which is as low as 2.73 m $\Omega$ , and this allows to achieve the waveforms shown in Fig. 9. Here, the red traces are the voltage across the capacitors and the blue traces are the voltages across the external resistances connected in series to the output filter the capacitors. Fig. 8 plots were acquired at a 50 mV/div scale so that the red traces show that the peak-to-peak values of the voltages across the capacitances are 236 mV in Fig. 9(a), 197 mV in Fig. 8(b), and 192 mV in Fig. 9(c). Similarly, the blue traces, which are the plot of the voltages measured across the resistances are 85 mV in Fig. 8(a), 196 mV in Fig. 9(b), and 285 mV in Fig. 8(c). These values are summed up in Table IV. The percent errors among theoretically predicted values of the voltage ripples and those experimentally measured are given in Table V. All the errors shown in Table V are below the tolerances values of commercially available capacitors and, therefore, the results given by equations which have been theoretically derived in Section II are validated by the experimental measurements.

## VI. CONCLUSION

An expression for the ripple voltage in terms of the capacitance and the equivalent series resistance has been derived 8

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS

for Buck, Forward, Zeta, and Cuk PWM DC-DC power converters with an LCR second-order output filter operated in CCM. The proposed analysis neglects the equivalent series inductance, since this condition is verified in most of the practical applications. The calculated results were in very good agreement with the simulated results. It has been shown how the filter capacitance should be increased as the equivalent series resistance increases at a required ripple voltage. Capacitors are not made to obey the relationship given by (19). However, the presented theory may provide a useful guideline for selection of a filter capacitor in the design of an LCR low-pass output filter, used in Buck, Forward, Zeta, and Cuk PWM DC-DC converters, regardless of the good design procedures such as implementing the output capacitor through a combination of several parallel elements. The presented results can be extended to Buck-derived converters, such as half-bridge, full-bridge, and push-pull PWM converters. The frequency of these converters is twice that of the switching frequency of power transistors.

#### REFERENCES

- D. Czarkowski and M. K. Kazimierczuk, "Static- and dynamic-circuit models of PWM buck-derived DC–DC converters," *IEE Proc. G Circuits, Devices Syst.*, vol. 139, no. 6, pp. 669–679, Dec. 1992.

- [2] M. K. Kazimierczuk, Pulse-Width Modulated DC-DC Power Converters, 2nd ed. Chichester, U.K.: Wiley, 2016, pp. 33–39.

- [3] J. J. Jozwik and M. K. Kazimierczuk, "Dual SEPIC PWM switchingmode DC/DC power converter," *IEEE Trans. Ind. Electron.*, vol. 36, no. 1, pp. 64–70, Feb. 1989.

- [4] A. Kouchaki and M. Nymand, "Analytical design of passive LCL filter for three-phase two-level power factor correction rectifiers," *IEEE Trans. Power Electron.*, vol. 33, no. 4, pp. 3012–3022, Apr. 2018, doi: 10.1109/TPEL.2017.2705288.

- [5] C. Nardi, C. M. O. Stein, E. G. Carati, J. P. Costa, and R. Cardoso, "A methodology of LCL filter design for grid-tied power converters," in *Proc. IEEE 13th Brazilian Power Electron. Conf. 1st Southern Power Electron. Conf. (COBEP/SPEC)*, Nov. 2015, pp. 1–5, doi: 10.1109/COBEP.2015.7420101.

- [6] W. Yi, L. Heming, S. Xinchun, and Z. Ling, "Harmonic analysis and filter design for medium-voltage multilevel PWM inverters," in *Proc.* 5th Int. Conf. Power Electron. Drive Syst. (PEDS), 2003, p. 531, doi: 10.1109/PEDS.2003.1282895.

- [7] W.-T. Fan, K. K.-F. Yuen, and H. S.-H. Chung, "Power semiconductor filter: Use of series-pass device in switching converters for filtering input current harmonics," *IEEE Trans. Power Electron.*, vol. 31, no. 3, pp. 2053–2068, Mar. 2016, doi: 10.1109/TPEL.2015. 2440393.

- [8] D. Ochoa, A. Lázaro, M. Sanz, A. Barrado, and J. Rodriguez, "Analysis and extension of the canonical model applied to DC–DC converters with input filter and output post-filter," in *Proc. IEEE Appl. Power Electron. Conf. Exposit. (APEC)*, Mar. 2020, pp. 3008–3013, doi: 10.1109/APEC39645.2020.9124260.

- [9] N. A. Keskar and G. A. Rincon-Mora, "A fast, sigma-delta (ΣΔ) boost DC-DC converter tolerant to wide LC filter variations," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 55, no. 2, pp. 198–202, Feb. 2008, doi: 10.1109/TCSII.2007.910801.

- [10] M. Sobaszek, "Self-tuned class-D audio amplifier with post-filter digital feedback implemented on digital signal controller," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 3, pp. 797–805, Mar. 2020, doi: 10.1109/TCSI.2019.2955064.

- [11] N. Beohar, V. N. K. Malladi, D. Mandal, S. Ozev, and B. Bakkaloglu, "Online built-in self-test of high switching frequency DC–DC converters using model reference based system identification techniques," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 2, pp. 818–831, Feb. 2018, doi: 10.1109/TCSI.2017.2739479.

- [12] V. P. Galigekere and M. K. Kazimierczuk, "Analysis of PWM Z-source DC–DC converter in CCM for steady state," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 4, pp. 854–863, Apr. 2012, doi: 10.1109/TCSI.2011.2169742.

- [13] S. Z. Lüleç, D. A. Johns, and A. Liscidini, "A third-order integrated passive switched-capacitor filter obtained with a continuoustime design approach," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 10, pp. 3643–3652, Oct. 2019, doi: 10.1109/TCSI.2019. 2914638.

- [14] Z. Yao and L. Xiao, "Push-pull forward three-level converter with reduced rectifier voltage stress," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 10, pp. 2815–2821, Oct. 2010, doi: 10.1109/TCSI.2010.2047746.

- [15] A. Cantillo, A. De Nardo, N. Femia, and W. Zamboni, "A unified practical design method for capacitors of switching converters," *IEEE Trans. Ind. Electron.*, vol. 58, no. 8, pp. 3521–3536, Aug. 2011, doi: 10.1109/TIE.2010.2084050.

- [16] X. Li, X. Zhang, and F. Lin, "Design of LC filter for boost converter with the considerations of efficiency and power density," in *Proc. IECON* 46th Annu. Conf. IEEE Ind. Electron. Soc., Oct. 2020, pp. 2846–2849, doi: 10.1109/IECON43393.2020.9254758.

- [17] Aluminum Electrolytic Capacitors Radial Lead Type Data Sheet, Panasonic Ind., Kadoma, Japan, Jun. 2022.

- [18] Multilayer Ceramic Chip Capacitor Data Sheet, TDK, Tokyo, Japan, Feb. 2021.

- [19] A. I. Pressman, Switching Power Supply Design, 2nd ed. New York, NY, USA: McGraw-Hill, 1998.

- [20] A. I. Pressman, K. Billings, and T. Morey, *Switching Power Supply Design*, 3rd ed. New York, NY, USA: McGraw-Hill, 2009.

- [21] Surface Ceramic Mount Device Capacitors, Kyocera AVX, Fountain Inn, CA, USA, 2022.

Marian K. Kazimierczuk (Life Fellow, IEEE) received the M.S., Ph.D., and D.Sc. degrees in electronics engineering from the Department of Electronics, Warsaw University of Technology, Warsaw, Poland, in 1971, 1978, and 1984, respectively. From 1972 to 1978, he was a Teaching and Research Assistant at the Department of Electronics, Institute of Radio Electronics, Warsaw University of Technology, where he was an Assistant Professor from 1978 to 1984. In 1984, he was a Project Engineer with Design Automation Inc., Lexington,

MA, USA. From 1984 to 1985, he was a Visiting Professor with the Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA. Since 1985, he has been with the Department of Electrical Engineering, Wright State University, Dayton, OH, USA, where he is currently an University Distinguished Professor. He has authored/coauthored more than 250 peer-reviewed journal articles and 270 conference papers, and seven books, such as the Electronic Devices: A Design Approach (Prentice Hall/Pearson, 2004), the Laboratory Manual for Electronic Devices: A Design Approach (Prentice Hall/Pearson, 2004), the Resonant Power Converters (Wiley, Second Edition, 2011), the Pulse-Width Modulated DC-DC Power Converters (Wiley, Second Edition, 2016), the Laboratory Manual for Pulse-Width Modulated DC-DC Power Converters (Wiley, 2016), the High-Frequency Magnetic Components (Wiley, Second Edition, 2014), and the RF Power Amplifiers (Wiley, Second Edition, 2015). He holds eight patents. His research interests include high-frequency highefficiency switching-mode tuned power amplifiers, resonant and pulse-width modulated dc-dc power converters, dc-ac inverters, high-frequency softswitching rectifiers, electronic ballasts, modeling and control of converters, new converter topologies, renewable energy sources, power factor correction, and wide-band gap power semiconductor devices. He received the Presidential Research, Teaching, and Service Awards as well as the Trustee's Award from Wright State University. He won The Best Paper Award from IET Power Electronics in 2012. He has served as an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS and Journal of Circuits, Systems and Computers. He serves as an Associate Editor for the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, International Journal of Circuits Theory and Applications, and IET Circuits, Devices and Systems.

Gabriele Maria Lozito (Member, IEEE) was born in Rome, Italy, in 1984. He received the master's degree in electronics engineering and the Ph.D. degree in soft-computing techniques on embedded systems from Roma Tre University, Italy, in 2010 and 2016, respectively. He is currently an Assistant Professor with the University of Florence on the main research topic of circuit modeling for renewable energy applications. He was a Visiting Researcher at the National Physical Laboratory (NPL), London. He has published his research in

several international journals, including IEEE TRANSACTIONS. His research interests include machine learning and optimization algorithms, embedded devices implementations, and magnetic materials modeling. He has served as the Chair for IEEE Congresses.

Alberto Reatti (Member, IEEE) received the degree in electronics engineering from the University of Florence, Italy, in 1988, and the Ph.D. degree from the University of Bologna, Bologna, Italy, in 1993. In 1992, he was an Associate Researcher with the Department of Electrical Engineering, Wright State University, Dayton, OH, USA. He has been an Associate Professor with the Department of Information Engineering, University of Florence, since 2000. He is responsible for agreements of cultural and scientific cooperation at the Department of Information

Engineering and the Head of the Patent and Technology Transfer Board, University of Florence. He has authored or coauthored more than 110 papers, including those appeared in IEEE TRANSACTIONS and journals. He holds two patents. His current research interests include high-frequency, resonant and pulse-width modulated dc–dc power converters, dc–ac inverters, modeling and control of converters, high-frequency magnetic devices, renewable power sources, energy saving, wireless power transfer, and investigations on reliability of switching power converters. He has served as the Chairperson for the Power Electronic and Power Systems Committee of IEEE CAS Society.

Fabio Corti (Member, IEEE) received the M.S. degree in electrical and automation engineering and the Ph.D. degree in industrial engineering from the University of Florence, Italy, in 2016 and 2019, respectively. He is currently a Post-Doctoral Research Fellow with the University of Perugia. His research interests include modeling and control of DC–DC PWM and resonant converters, wireless power transfer, and electric vehicle powertrain.